I'm trying to use the new Zephyr high-performance support for the 5340 DK flash chip but so far, no luck.

Here is the relevant section of my overlay:

&qspi {

mx25r64: mx25r6435f@0 {

mxicy,mx25r-power-mode = "high-performance";

};

};I'm trying to use the new Zephyr high-performance support for the 5340 DK flash chip but so far, no luck.

Here is the relevant section of my overlay:

&qspi {

mx25r64: mx25r6435f@0 {

mxicy,mx25r-power-mode = "high-performance";

};

};Hi,

The binding is currently only available for the Zephyr spi_nor driver (relevant commit), not qspi_nor, and I am not sure you will be able to get better IO performance if you had to switch from QSPI to SPI.

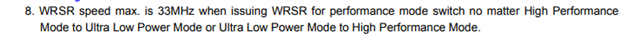

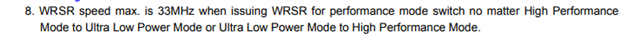

To get the most out of the performance mode, it seems like you would have to set the QSPI clock frequency to 32 MHz (closest you can get to 33 MHz with the clock divider) when writing the WRSR register. From the datasheet:

Then when the flash is configured, increase the QSPI clock to 48 MHz (next step up is 96MHz) which is the closest you can get to the 80 MHz max frequency supported by the flash IC in high performance mode.

Best regards,

Vidar

Hi,

The binding is currently only available for the Zephyr spi_nor driver (relevant commit), not qspi_nor, and I am not sure you will be able to get better IO performance if you had to switch from QSPI to SPI.

To get the most out of the performance mode, it seems like you would have to set the QSPI clock frequency to 32 MHz (closest you can get to 33 MHz with the clock divider) when writing the WRSR register. From the datasheet:

Then when the flash is configured, increase the QSPI clock to 48 MHz (next step up is 96MHz) which is the closest you can get to the 80 MHz max frequency supported by the flash IC in high performance mode.

Best regards,

Vidar

Thanks for the quick response. I previously tried increasing the frequency to 32MHz, but I'm not really seeing an increase in performance. I suppose it could be something else related to using LittleFS but it does seem weird.

I guess I'm a little confused, b/c the documentation does seem to call out nordic qspi: https://docs.zephyrproject.org/latest/build/dts/api/bindings/mtd/nordic,qspi-nor.html

Although admittedly, I'm not sure to which version this is referring.

Jeffrey Haynes said:Thanks for the quick response. I previously tried increasing the frequency to 32MHz, but I'm not really seeing an increase in performance. I suppose it could be something else related to using LittleFS but it does seem weird.

I too would have expected some performance improvement with this frequency. But it could be like you indicated that the bottleneck is elsewhere. It is probably easier to test the QSPI/flash performance without a filesystem. For instance, with the JEDEC SPI-NOR Sample.

Jeffrey Haynes said:I guess I'm a little confused, b/c the documentation does seem to call out nordic qspi: https://docs.zephyrproject.org/latest/build/dts/api/bindings/mtd/nordic,qspi-nor.html

I was surprised to see this in the documentation. git blame does not reveal when this property was added/removed. It is not included in current main or previously tagged releases of Zephyr upstream, at least (https://github.com/nrfconnect/sdk-zephyr/blob/main/dts/bindings/mtd/nordic%2Cqspi-nor.yaml). And when I look at the QSPI driver (https://github.com/nrfconnect/sdk-zephyr/blob/main/drivers/flash/nrf_qspi_nor.c ) there is no references to this mode.

Interesting. Ok, thanks. I'm considering moving to non-FS mode for our application anyway so maybe I'll just go that route. Thanks!

Btw, looking back at it I think there may have been a 15-20% speed improvement at the higher frequency.