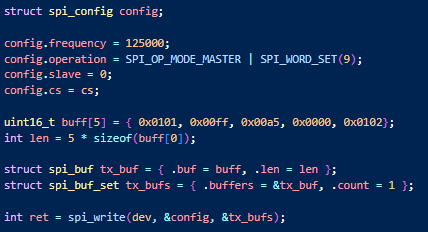

I am integrating the Zephyr SPI Bitbang example located here zephyr/samples/drivers/spi_bitbang at main · zephyrproject-rtos/zephyr · GitHub. The frequency of 12.5KHz is configured in code as shown in the image below

Altering this frequency has no effect on the speed of transmission when viewed with a Logic Analyzer. I would like to adapt the program to utilize the maximum SPI frequency available to me on the board, which is 32MHz.

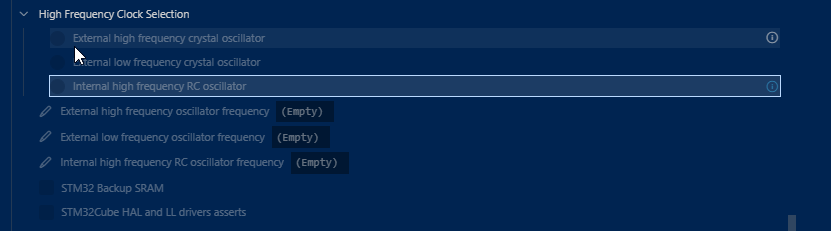

Also, if I try to use the Kconfig to add the option for a High Frequency Clock, the option is not available to be selected as seen below:

nRF Connect SDK Version: 2.1.0

Zephyr version: 3.1.99