When an interrupt is raised, doesn't the peripheral's bit in a ISPR get set, which should be manually cleared in the ICPR?

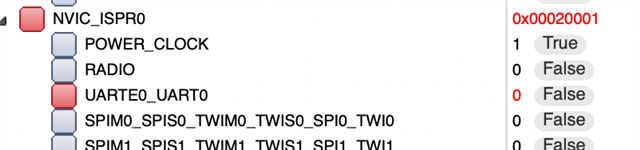

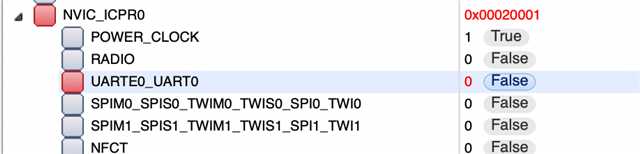

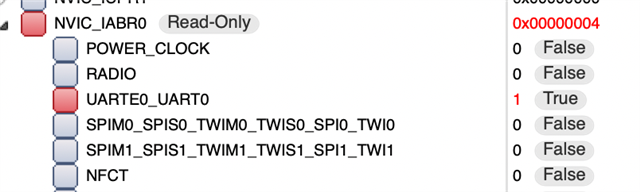

For UART0, I see the following bits getting modified.

ISPR0 and ICPR0 seem to get modified to 0 but I'd expect the bit in ISPR to be set and ICER0 to yet to be set (should be done in the interrupt handler no)? Are these registers set somewhere in nordic lower layer prior to reaching UARTE0_UART0_IRQHandler (though I don't see in the call stack)?

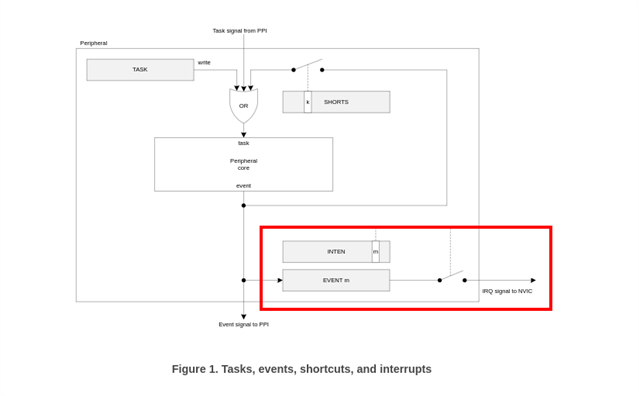

Secondly, in STM32 they call it EXTI but here, INTENSET is somewhat similar in the sense that it's connected to NVIC? Ans of course NVIC register ISER would need to be set in addition to iNTENSET