Hi,

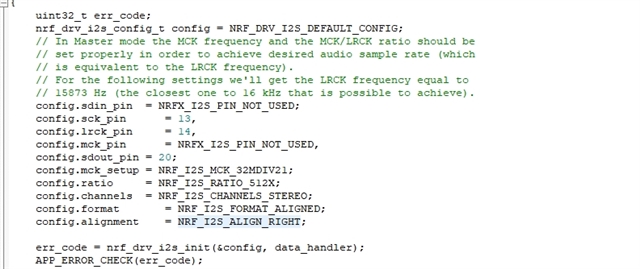

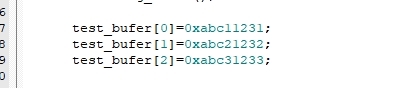

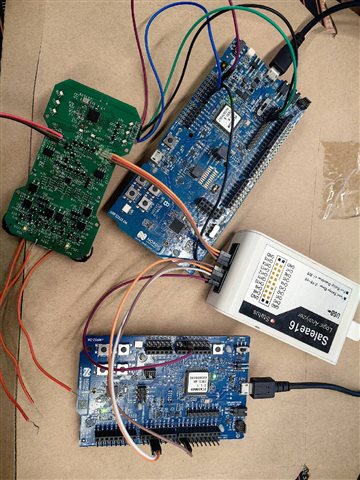

I used the example in SDK_17.1 and NRF52DK board to test I2S.

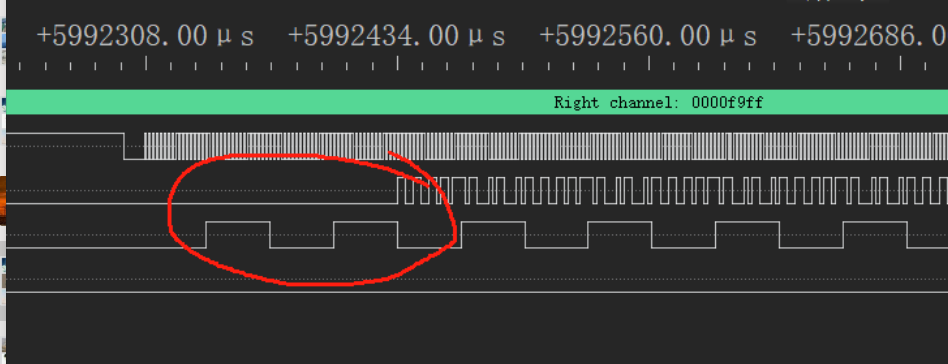

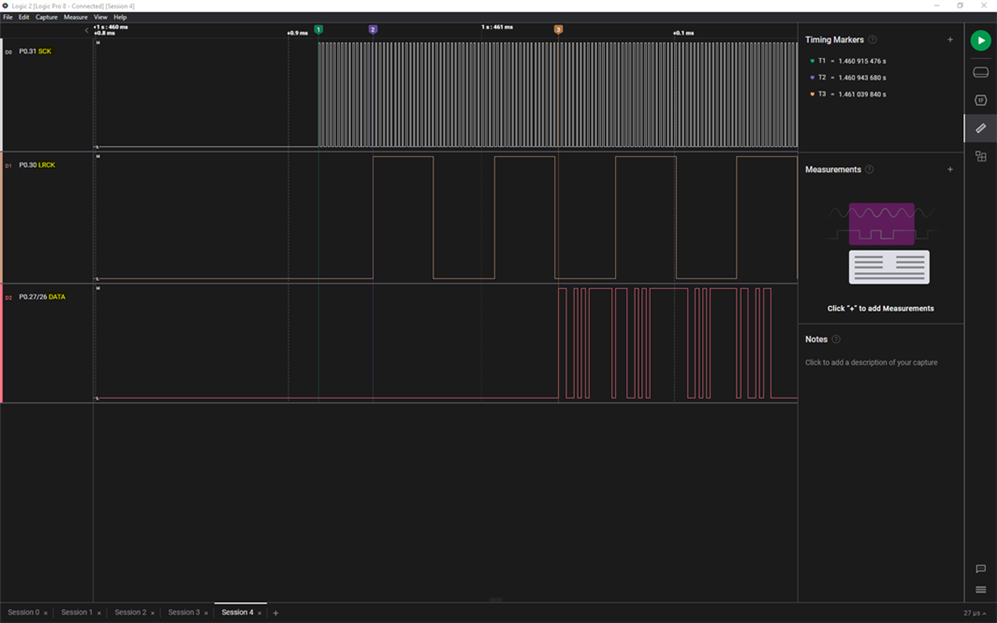

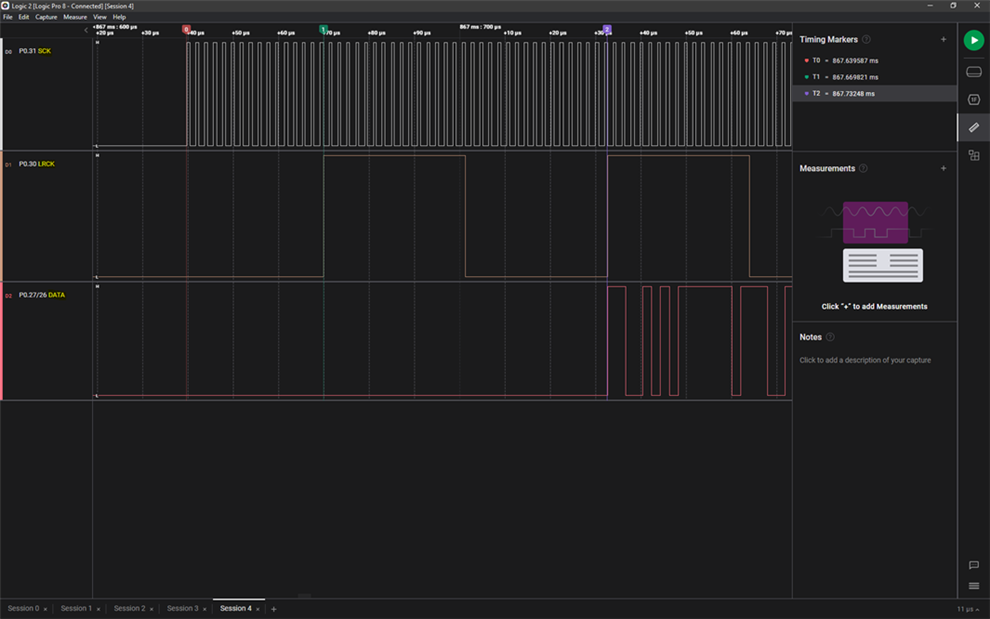

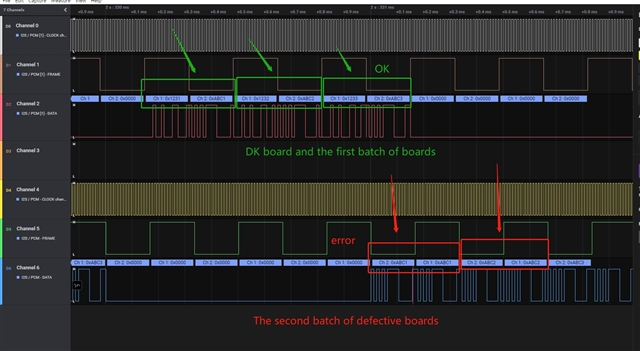

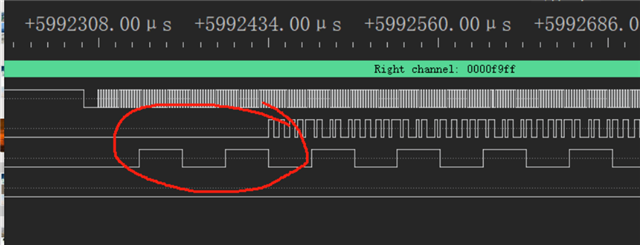

The logical analysis instrument picked up the following waveform:

As you can see, the data was initially absent, causing a problem with the data input pin level on the I2S hardware I plugged in. What I want to know is how I should configure the data to be transferred from the very beginning.

Best regards,

Stars