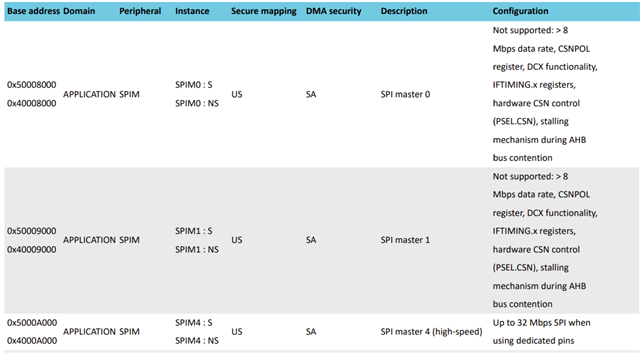

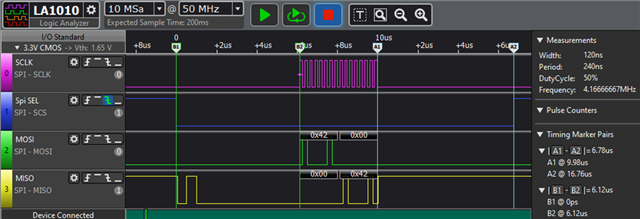

I'm trying to access the nRF5340 over SPI Slave from another processor who is SPI Master. Running a simple "looback test" between an nRF5340 SPI Master and SPI Slave seems to work fine but when I try it with the external processor's SPI Master the data sent on the MOSI line isn't read correctly by the nRF5340 SPI Slave. Taking a snapshot with the Logic analyzer produces some interesting results. The loopback tests I ran is too1/ncs-spi-master-slave-example (github.com) and it works fine (although it does use the deprecated call spi_transeive_async()). However, I notice about a 7 microsecond delay between the SS going low and the SCK transitions. During this time MOSI is idle but MISO toggles

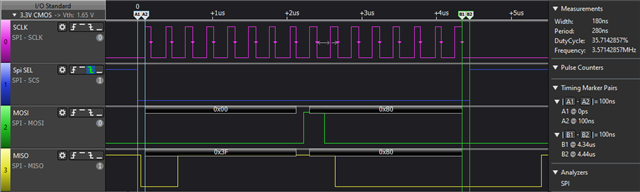

When I try my own SPI Master there's only about 70ns delay between SS and SCK. However, everything is shifted in terms of when SPI Slave starts reading the data. I ran a "walking ones" tests and found that on a 16 bit transfer only bits 7-14 are detected by SPI Slave which reads them as bits 8-15. Also the MISO line still toggles, now being read as 0x3F 0x80

Is there any way to remove this delay requirement? 14usec of wasted time per SPI transaction will create very low transfer rates plus the only way I can perform the delay on the SPI Master side is to replace the SS signal with a GPIO that I toggle manually before making the SPI transfer call.

Here is how I am setting up the SPI Slave port in my device tree overlay file