Hello, I have the following problem. I am total newbie in nRF programming, so I have minimal knowledge about that hardware.

I have bought nRF5340-DK earlier, firmware on it is working properly.

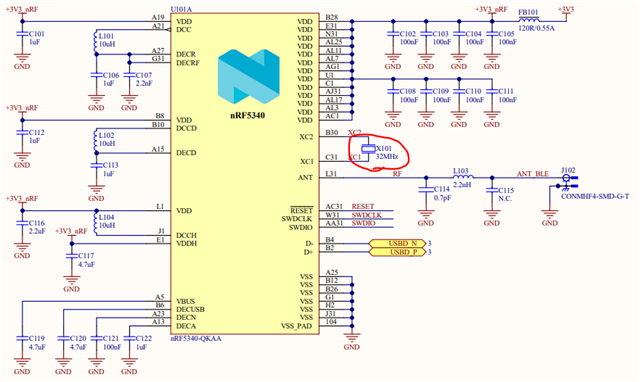

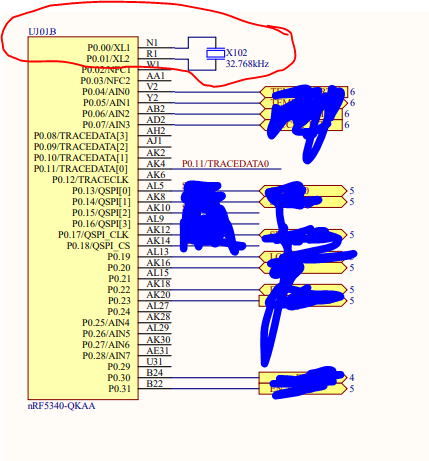

Then there was created custom hardware for sme that has nRF5340 chip onboard, exactly part number NRF5340-QKAA-R.

There are programming pins onboard next to the chip, that I can use for programming it with following pinout:

So for my purpose there were used pins such as: 3V3, GND, SWDIO, SWDCLK and RESET.

I have used ST-link V2 interface that I have reflashed to J-link, so it acts as J-link now.

I have also downloaded J-link installation, drivers.

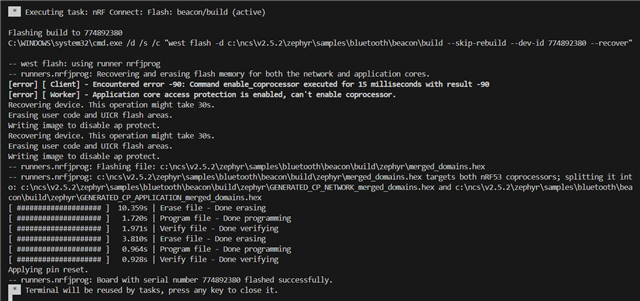

So I have created build. Then I flashed it to the nRF chip.

There I had to click to overwrite, as it has protection for writing new firmware (same bahaviour as in case of NRF5340-DK devkit.

Firmware was uploaded, also verification was performed, everything ended with status OK.

But firmware is NOT running. I don't see any Bluetooth broadcast from this chip.

From devkit I see it immediately after programming.

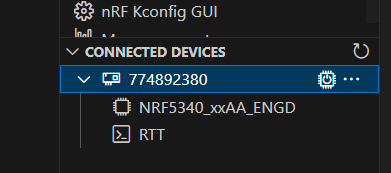

When I open VS Code from nRF Connect - Toolchain,

I see J-link interface there and also when I click on it, I see nRF5340 there.

I don't have any COM port in Terminal tab, so I cannot see what board is doing.

About that P0.11/TRACEDATA0 pin, for what it is used? Some kind of debug or serial interface?

I am thinking there I need to upload bootloader or something, but dont know why. Sample named bluetooth can't be compiled for my CPU target.

Totally I haven't found what I need to download or how to upload bootloader. There is simply no guide for this. Or can it be something else? Please help, how to fix it.

Everything looks like VS Code is communicating with microcontroller, as I see verification and it is okay, so firmware was uploaded into nRF's flash memory.

Tomorrow I can add some output from VS Code during upload etc.

Firmware was identical for devkit or for standalone chip, no changes there.