Hello,

I am using the nRF52840 as modbus client and experiencing some missing bytes during communication (RTU mode) when using a high baud rate (460800). This tends to happen more often when requesting a big chunk of data at once, but does also happen when requesting only two registers (4 bytes).

I opened an issue ticket on github (Link to github) describing this problem with some comments on how to mitigate. However, the problem is still present

Can someone try to give me any input?

I do also have a few questions related to UARTE in interrupt driven mode (as I am using it):

- it is stated in the uart (not uarte) documentation under 6.33.5 of the product specification that "The UART receiver chain implements a FIFO capable of storing six incoming RXD bytes before data is overwritten.". However, I did not find any information about this hardware FIFO size when it comes to UARTE. Is it the same (6)?

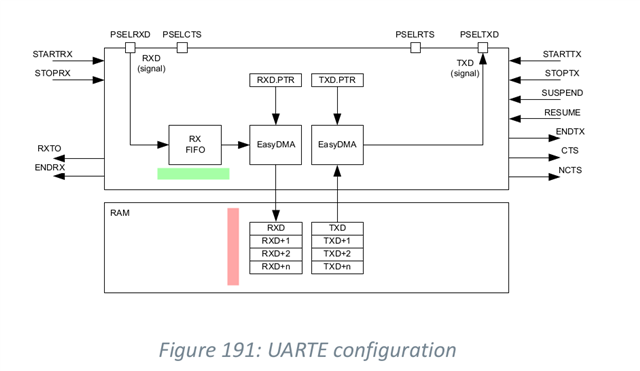

- is the following correct? The data will be received in the hardware FIFO buffer of UARTE (of depth x?), then it will be copied with EasyDMA to be placed in RAM in a buffer of size 1 as in zephyr/drivers/serial/uart_nrfx_uarte.c (see code below). The modbus driver does then implement a cb_handler_rx that gets triggered when bytes are received and copies them from the previous RAM buffer one by one to another driver specific buffer of custom size. Is this correct?

nrf_uarte_rx_buffer_set(uarte, data->rx_data, 1);

- When I am missing a byte, I was able to check the ERRORSRC register to see that an overrun has occured (value of the register =1). How much time do I have before getting an overrun?

- When does the overrun occur: is it when the first bit is received while data still in FIFO or in RAM buffer?

I am looking forward to your answers and input on how to solve the missing bytes problem.

FYI: the use of Hardware flow control is unfortunately not an option in our case, as the server does not support it. Moreover, I am not able of reducing the baud rate as this is constant (from the server side as well).