When I use a power supply, (3.0Volts-60mA limitation) with the DevKit boards nRF51 or nRF52 the input voltage is clamped at around 2.0 V and the current is 60mA : the SoC doesn’t start.

By increasing the current limitation, step by step, the SoC start, with the current threshold of 80mA.

After the start up, the current of the devKit is low as expected. (With the software ble_peripheral>ble_app_hts s110 for nRF51 or s132 for nRF52).

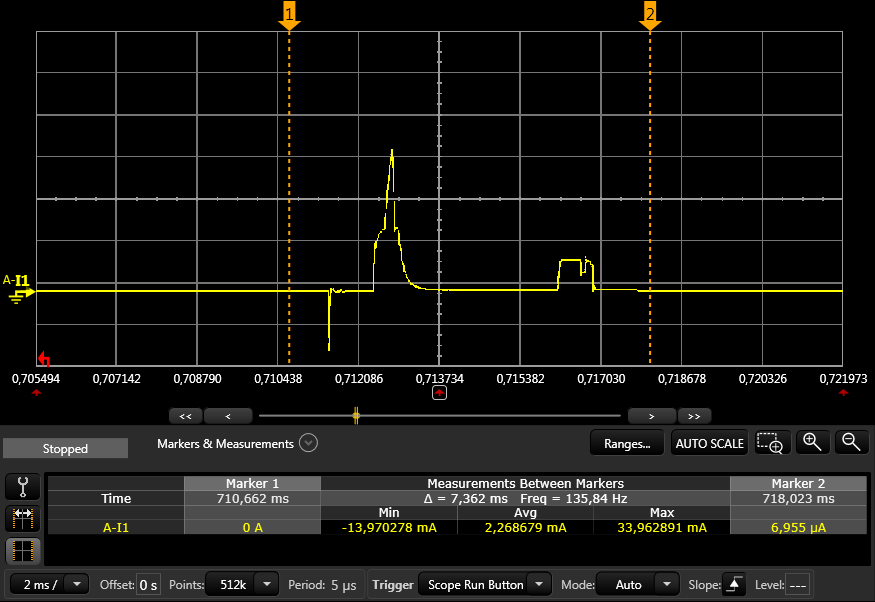

I've checked the inrush current with a scope. I've seen a pulse of 500mA and 30µs width .