Hi,

I'm using the PPI component to generate 8MHz GPIO signal. this signal is an input for power amplifier analog RF transmitter.

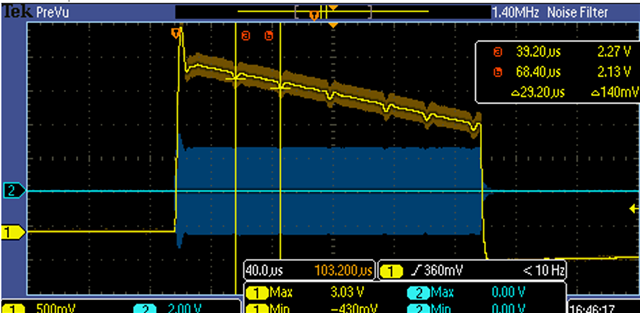

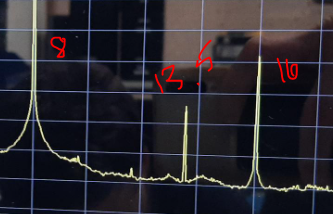

While the digital 8MHz signal looks fine, we are noticing some bumps every 40 us in the RF analog signal. when trying to use the SPI clock to create the 8MHz signal the bumps are eliminated and we get a clean signal.

As the PPI input clock is 16MHz, I was wondering if theoretically its capable to create a digital 8MHz signal? that means that the GPIO should be toggled every single clock, is that an overkill in terms of performance for the PPI or should it be able to handle this task?

The bumps were also reproduced with the DK evaluation board to generate the 8MHz signal, see bump in the image below: