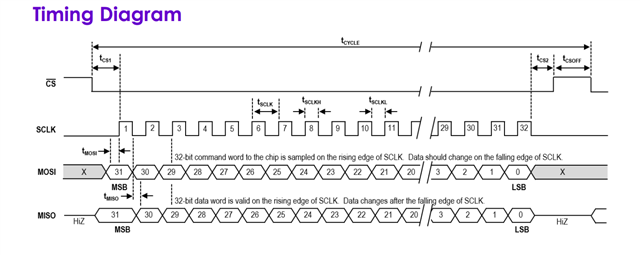

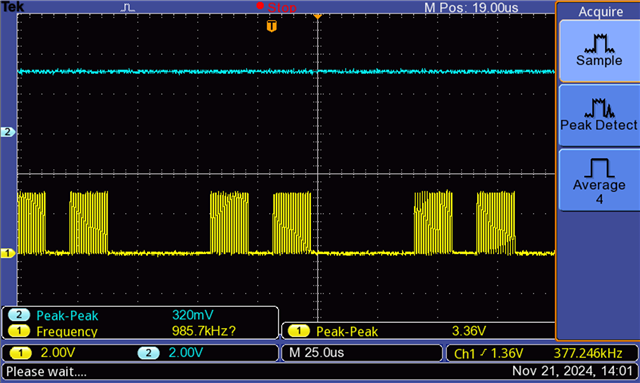

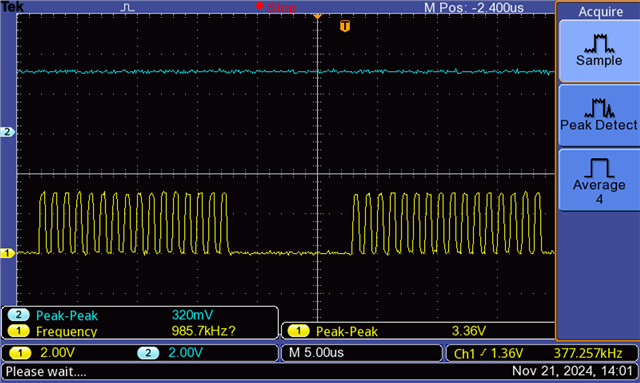

We are developing on the nRF52 Development Kit (nRF52 DK) for the nRF52832 SoC. Our application involves a 4-wire pipelined SPI communication with the Intan RHS2116 chip. According to the RHS2116 documentation (page 30, Picture 1), the SPI connection is configured such that the RHS2116 automatically outputs data two command cycles after a command is sent. This means that by the time we reach the 3rd command, there will be output data on MISO that we need to receive concurrently as the master (nRF52832) transmits the next command via MOSI.

Our challenge is with the nRF Connect SDK and Zephyr OS: specifically, it’s unclear from Zephyr’s SPI library documentation if the spi_transceive function performs read and write operations within the same command cycle, which is required to meet the pipelined data flow of the RHS2116.

Could you confirm if spi_transceive in the nRF Connect SDK supports simultaneous read/write operations in the same cycle? Additionally, if there are configurations or alternative methods recommended for achieving this synchronized SPI communication with the nRF52832, we would appreciate any guidance.