I have been working for a while on a project that requires the maximum possible speed from both app core and SPIM4 peripheral. To do so, I set the app core clock speed to 128MHz executing these lines as first operation in main function:

for what concerns the SPIM4 configuration, in the overlay file I have:

in main function, instead I execute this function after setting the app core clock freq. to 128MHz:

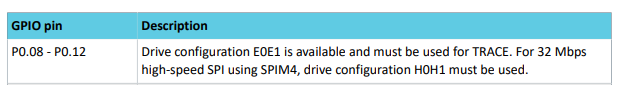

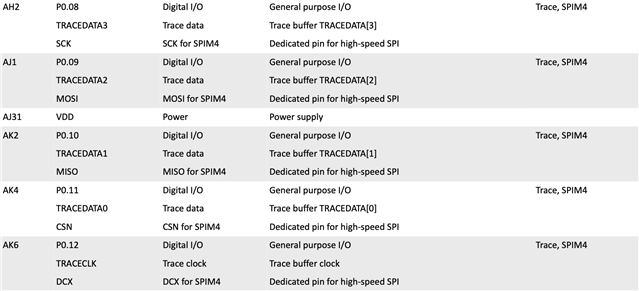

- how to make SPIM4 work at 32MHz?