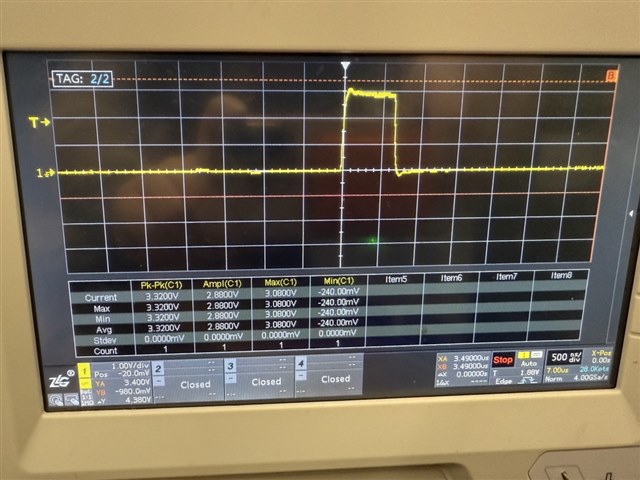

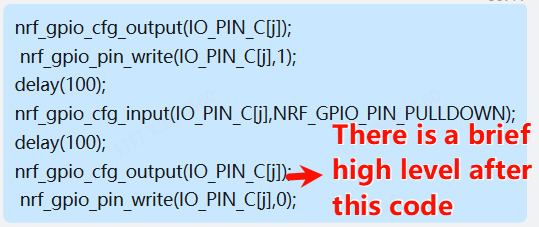

Is my following operation, first output high, and then configure as input, and then in the output low, this time in the output low here nrf_gpio_cfg_output(IO_PIN_C[j]); This one has a brief high level.

We look at the source routines are output and then write, so the understanding is nrf_gpio_cfg_output(IO_PIN_C[j]); Just configuration, the actual output level is after nrf_gpio_pin_write(IO_PIN_C[j],0) is executed. Is there a misunderstanding here?