Hi all,

In the PDF version of nRF54L PRELIMINARY DATASHEET v0.8, in chapter

9.1 Debug access port:

in table 65: Access port overview

is listed AUX access port of AHB-AP with AP ID 1.

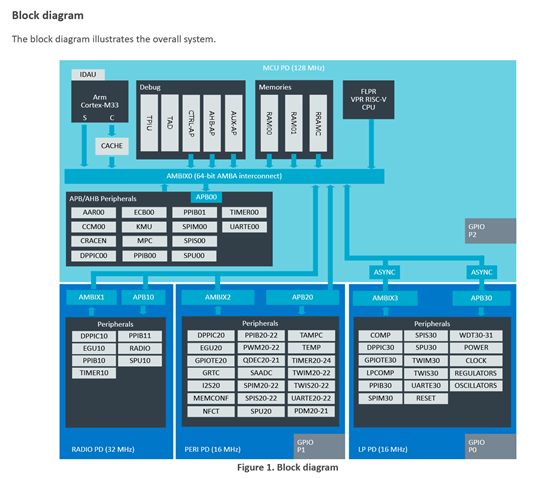

Figure 160: Debug and trace overview

shows AUX-AP connected to VPR trough AMBIX0 block.

In table 66 in chapter 9.2 Access port protection:

Access port protection overview registers UICR.AUXAPROTECT, TAMPC.PROTECT.AP[0].DBGEN

are described as "These registers control the generation of the AHB-AP DBGEN signal,

which controls debug access to the VPR AHB-AP. This is used to provide debug capability for VPR."

But there is no other info where any VPR debugging resides in AUX-AP memory space.

Moreover I didn't find any readable address in AUX-AP.

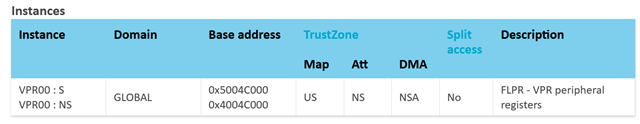

FLPR/VPR RISC-V coprocessor DM (debug module) registers are exposed @ 0x4004C000 / 0x5004C000 of APP-AP (AP ID 0) address space as described

in 8.26.1 Registers

What is AUX-AP for? Is possible to use it for RISC-V DM access?