Hi all,

I need to generate two 1 MHz signals with opposite phases. However once I configure the decode mode as "Individual" I don't have output signals. In case of "Common" mode, I have two same output signals but this is not what I want. Under debugger I have different register values especially for EVENTS_SEQxxx.

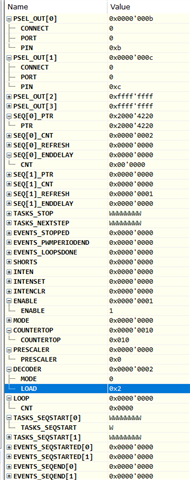

1. Individual mode

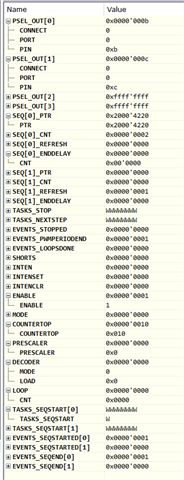

2. Common mode

Here is the code:

Thanks for your help.

BR,

Hulu