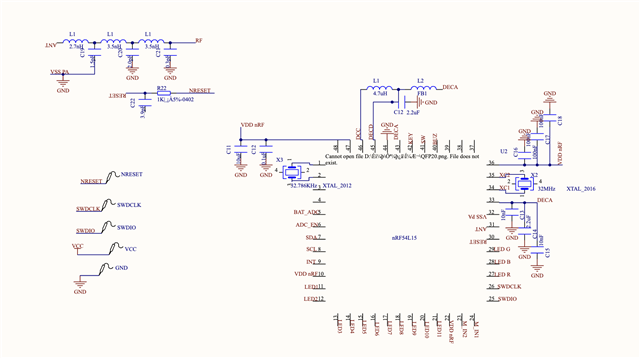

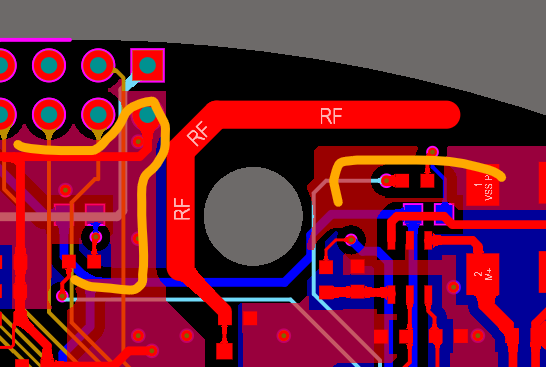

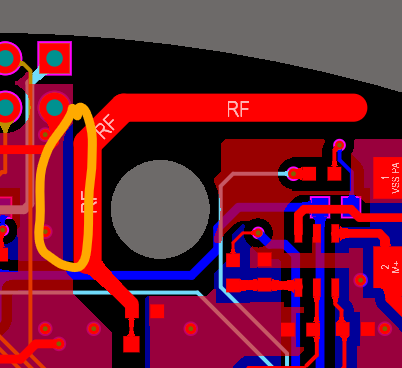

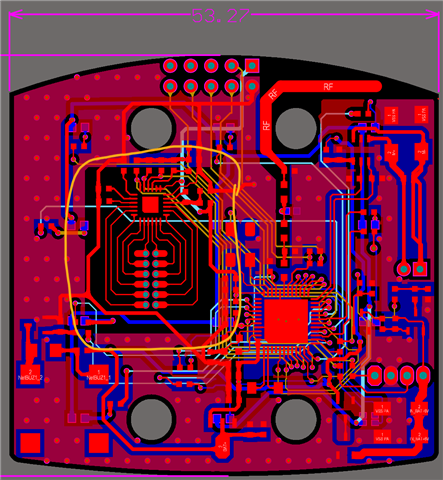

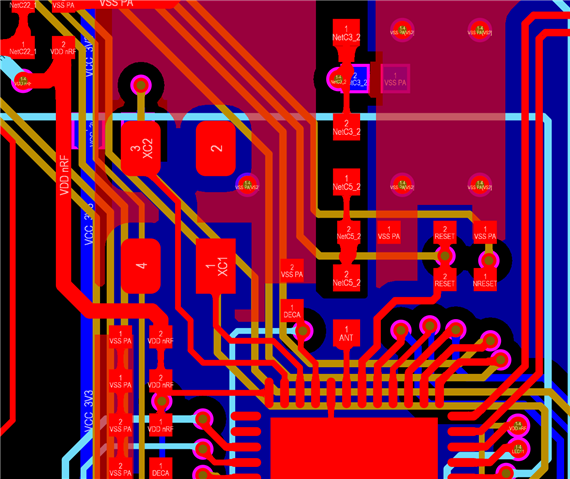

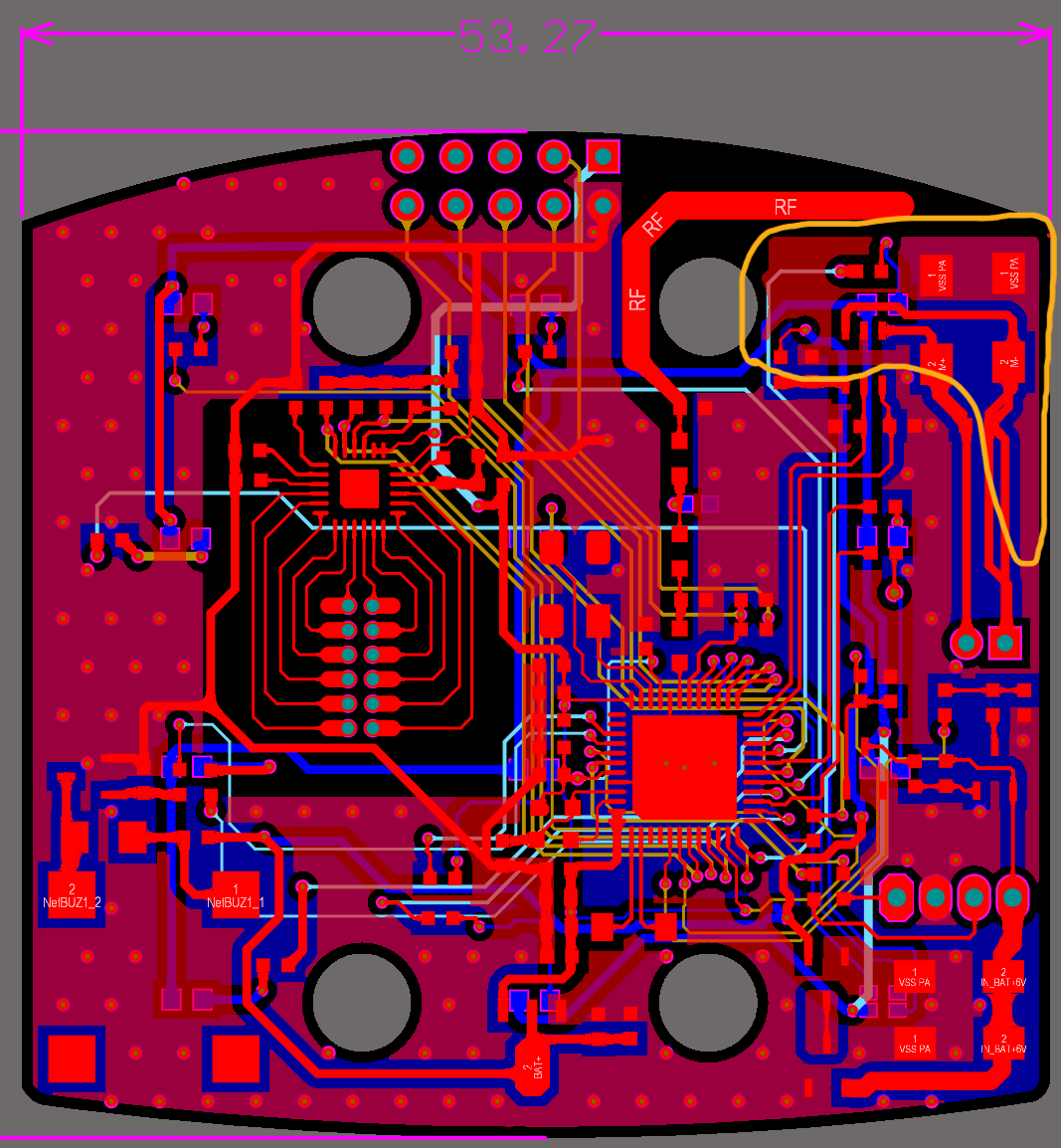

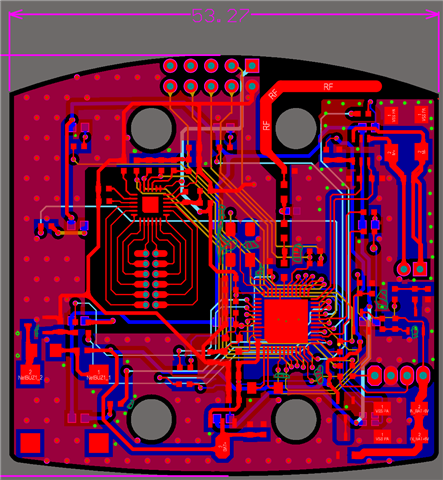

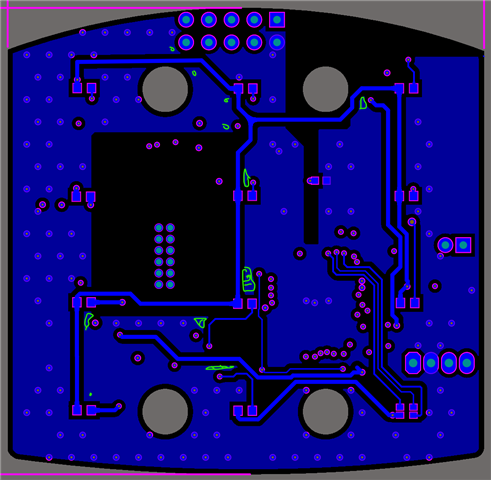

Hi, I would like to have some suggestions on my PCBA design for nrf54L15 chip. Please review it and give some suggestion moving forward. I am making this PCB to use this with matter-over-thread products. Since nrf54L15 is a pretty new product, I couldn't find many reference designs online. I mostly used the reference designs provided by Nordic but have been struggle on the programming port design. Also does nordic have any recommendation on which Antenna I should use for this design?

Thanks