I am testing the Sleep idle current for the nRF52833QDAA module.

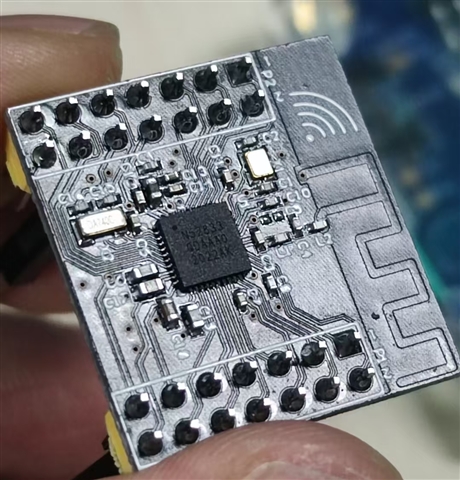

The module is nothing connected outside except the fundamental circuit as the attached picture shown.

And I am using a very simple code to turn the module to sleep idle mode in the main.

here is the code:

void disable_ram_retention(void) {

// Disable RAM retention for the desired RAM sections

// Add more sections as needed

NRF_POWER->RAM[0].POWERCLR = 0; // Disable RAM section 0

NRF_POWER->RAM[1].POWERCLR = 0; // Disable RAM section 0

NRF_POWER->RAM[2].POWERCLR = 0; // Disable RAM section 0

NRF_POWER->RAM[3].POWERCLR = 0; // Disable RAM section 0

NRF_POWER->RAM[4].POWERCLR = 0; // Disable RAM section 0

NRF_POWER->RAM[5].POWERCLR = 0; // Disable RAM section 0

NRF_POWER->RAM[6].POWERCLR = 0; // Disable RAM section 0

NRF_POWER->RAM[7].POWERCLR = 0; // Disable RAM section 0

}

int main(void)

{

disable_ram_retention();

while (true) {

__WFE(); // Wait for event

__SEV();

__WFE(); // Wait for event again to ensure we stay in sleep mode

}

}

void enable_ram_retention(void) {

// Enable RAM retention for the desired RAM sections

NRF_POWER->RAM[0].POWERSET = 1; // Disable RAM section 0

NRF_POWER->RAM[1].POWERSET = 1; // Disable RAM section 0

NRF_POWER->RAM[2].POWERSET = 1; // Disable RAM section 0

NRF_POWER->RAM[3].POWERSET = 1; // Disable RAM section 0

NRF_POWER->RAM[4].POWERSET = 1; // Disable RAM section 0

NRF_POWER->RAM[5].POWERSET = 1; // Disable RAM section 0

NRF_POWER->RAM[6].POWERSET = 1; // Disable RAM section 0

NRF_POWER->RAM[7].POWERSET = 1; // Disable RAM section 0

}

I find that there is totally no sleep idle current difference if I called enable_ram_retention or disable_ram_retention before enter sleep idle mode.

So How can I achieve the sleep idle mode current ( System ON, no RAM retention, wake on any event 1.1uA) without RAM retention according to the nRF52833 manual?

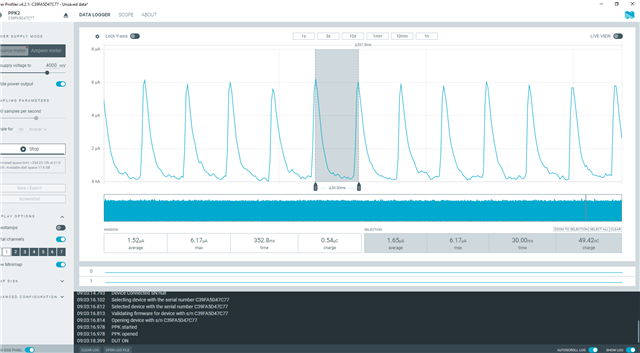

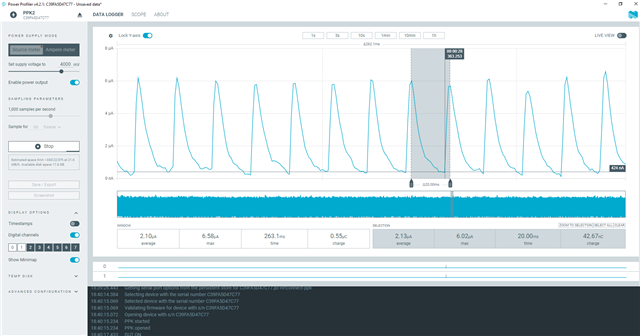

Right now it is only average 2uA, any help to achieve 1.1uA??

Thanks.