I've been able to flash consistently but I finally got my nrf5340 custom board working using Hight Voltage DC/DC by setting it to UICR_VREGHVOUT_VREGHVOUT_3V0, but when I tried to flash again with my Segger JLink after making some changes I get this:

-- west flash: using runner nrfjprog -- runners.nrfjprog: reset after flashing requested -- runners.nrfjprog: Flashing file: /Users/********/Projects/GitHub/********/pcb_test/build_dj_291/merged.hex [error] [ Client] - Encountered error -220: Command erase_file executed for 30136 milliseconds with result -220 [error] [ nRF53] - Failed while performing Erase operation on target address 340. -220: NVMC controller never gets ready. [error] [ nRF53] - Failed while erasing device. -220: NVMC controller never gets ready. [error] [ Worker] - NVMC controller never gets ready. ERROR: Operation failed due to timeout. Check the log messages for more details. NOTE: For additional output, try running again with logging enabled (--log). NOTE: Any generated log error messages will be displayed. FATAL ERROR: command exited with status 64: nrfjprog --program /Users/********/Projects/GitHub/********/pcb_test/build_dj_291/merged.hex --sectorerase --verify -f NRF53 --coprocessor CP_APPLICATION --snr *********

When I connect using jlinkexe I get:

Device "NRF5340_XXAA_APP" selected. Connecting to target via SWD ConfigTargetSettings() start ConfigTargetSettings() end - Took 23us InitTarget() start InitTarget() end - Took 1.74ms Found SW-DP with ID 0xFBB03477 DPIDR: 0x6BA22677 CoreSight SoC-400 or earlier AP map detection skipped. Manually configured AP map found. AP[0]: AHB-AP (IDR: Not set, ADDR: 0x00000000) AP[1]: AHB-AP (IDR: Not set, ADDR: 0x00000000) AP[2]: MEM-AP (IDR: Not set, ADDR: 0x00000000) AP[3]: MEM-AP (IDR: Not set, ADDR: 0x00000000) AP[0]: Core found AP[0]: AHB-AP ROM base: 0xE20FE200 CPUID register: 0x430FD216. Implementer code: 0x43 (???) Feature set: Mainline Cache: No cache Found Cortex-M33 r0p6, Little endian. FPUnit: 8 code (BP) slots and 2 literal slots Security extension: implemented Secure debug: enabled CoreSight components: ROMTbl[0] @ E20FE200 Memory zones: Zone: "Default" Description: Default access mode Cortex-M33 identified.

I did have logging running another time this is a segment of it:

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - read_u32

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_connect_to_device

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - is_connected_to_device

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_read_u32

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_invalidate_cache

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_ExecCommand("InvalidateCache", ...).

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.004ms returns 0x00

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_ReadMemU32(0x50039400, 0x1 Items)

[2025-Jun-08 15:23:02] [trace] [ JLink] - CPU_ReadMem(4 bytes @ 0x50039400)

[2025-Jun-08 15:23:02] [trace] [ JLink] - Data: 03 02 02 02

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 1.129ms returns 1 (0x1)

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - read_u32

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_connect_to_device

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - is_connected_to_device

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_read_u32

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_invalidate_cache

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_ExecCommand("InvalidateCache", ...).

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.003ms returns 0x00

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_ReadMemU32(0x50039400, 0x1 Items)

[2025-Jun-08 15:23:02] [trace] [ JLink] - CPU_ReadMem(4 bytes @ 0x50039400)

[2025-Jun-08 15:23:02] [trace] [ JLink] - Data: 03 02 02 02

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.811ms returns 1 (0x1)

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [error] [ Client] - Encountered error -220: Command erase_file executed for 30153 milliseconds with result -220

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - read_u32

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_connect_to_device

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - is_connected_to_device

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_read_u32

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_invalidate_cache

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_ExecCommand("InvalidateCache", ...).

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.003ms returns 0x00

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_ReadMemU32(0x50039400, 0x1 Items)

[2025-Jun-08 15:23:02] [trace] [ JLink] - CPU_ReadMem(4 bytes @ 0x50039400)

[2025-Jun-08 15:23:02] [trace] [ JLink] - Data: 03 02 02 02

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.969ms returns 1 (0x1)

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [error] [ nRF53] - Failed while performing Erase operation on target address 340.

-220: NVMC controller never gets ready.

[2025-Jun-08 15:23:02] [ info] [ nRF53] - {"amountOfSteps":0,"description":"Erasing non-volatile memory","message":"Failed while performing Erase operation on target address 340. \n-220: NVMC controller never gets ready.","operation":"erase_image","progressPercentage":0,"result":"fail","step":0}

[2025-Jun-08 15:23:02] [error] [ nRF53] - Failed while erasing device. -220: NVMC controller never gets ready.

[2025-Jun-08 15:23:02] [ info] [ nRF53] - {"amountOfSteps":0,"description":"Erase file","message":"Failed while erasing device. -220: NVMC controller never gets ready.","operation":"erase_image","progressPercentage":0,"result":"fail","step":0}

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 2.348ms

[2025-Jun-08 15:23:02] [error] [ Worker] - NVMC controller never gets ready.

[2025-Jun-08 15:23:02] [trace] [ Worker] - Command erase_file executed for 30146 milliseconds with result -220

[2025-Jun-08 15:23:02] [debug] [ nRF53] - close

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - is_connected_to_emu

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_IsOpen()

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.005ms returns 0x01

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_Lock()

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - close

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - disconnect_from_emu

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_disconnect_from_emu

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - is_connected_to_device

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_IsConnected()

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.002ms returns TRUE

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_is_debug_region_powered

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_read_debug_port_register

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_select_debug_port_register

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - Select AP 255, DP Bank 0, AP Bank 255

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_CORESIGHT_WriteAPDPReg(DP reg 0x02, 0x00000000)

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.405ms returns 0

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_CORESIGHT_ReadAPDPReg(DP reg 0x01)

[2025-Jun-08 15:23:02] [trace] [ JLink] - Value=0xF2020242

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.425ms returns 0

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - Disable trace before closing connection.

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_write_u32

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_write_debug_port_register

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_select_debug_port_register

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - Select AP 255, DP Bank 0, AP Bank 255

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_CORESIGHT_WriteAPDPReg(DP reg 0x02, 0x00000000)

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.466ms returns 0

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_CORESIGHT_WriteAPDPReg(DP reg 0x02, 0x00000000)

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.602ms returns 0

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_WriteU32(0xE000EDFC, 0x00000000)

[2025-Jun-08 15:23:02] [trace] [ JLink] - Debug reg: DEMCR

[2025-Jun-08 15:23:02] [trace] [ JLink] - CPU_WriteMem(4 bytes @ 0xE000EDFC)

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.906ms returns 0 (0x00000000)

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_is_debug_region_powered

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - Shortcut, lock is on and debug region is powered.

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - unpower_debug_and_system_regions

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_write_debug_port_register

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_select_debug_port_register

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_CORESIGHT_WriteAPDPReg(DP reg 0x01, 0x00000000)

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.515ms returns 0

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_HasError()

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_is_debug_region_powered

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_read_debug_port_register

[2025-Jun-08 15:23:02] [debug] [SeggerBackend] - ---just_select_debug_port_register

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLINK_CORESIGHT_ReadAPDPReg(DP reg 0x01)

[2025-Jun-08 15:23:02] [trace] [ JLink] - Value=0x02020242

[2025-Jun-08 15:23:02] [trace] [ JLink] - - 0.640ms returns 0

[2025-Jun-08 15:23:02] [trace] [ JLink] - JLI just got the UICR_VREGHVOUT_VREGHVOUT_3V0 running and am wondering if that could be it. I used this post as a reference which identifies if it is at the right level otherwise sets it using:

NRF_UICR->VREGHVOUT = (UICR_VREGHVOUT_VREGHVOUT_3V3 | ~UICR_VREGHVOUT_VREGHVOUT_Msk);

It's not showing as connected like it normally does in vs code:

This is what I get through jlinkexe:

SEGGER J-Link Commander V8.34 (Compiled May 14 2025 16:59:53)

DLL version V8.34, compiled May 14 2025 16:59:11

Connecting to J-Link via USB...O.K.

Firmware: J-Link V11 compiled Apr 1 2025 10:02:30

Hardware version: V11.00

J-Link uptime (since boot): 0d 00h 00m 15s

S/N: ********

License(s): RDI, FlashBP, FlashDL, JFlash, GDB

USB speed mode: High speed (480 MBit/s)

VTref=3.300V (fixed)

Type "connect" to establish a target connection, '?' for help

J-Link>connect

Please specify device / core. <Default>: NRF5340_XXAA_APP

Type '?' for selection dialog

Device>?

Please specify target interface:

J) JTAG (Default)

S) SWD

T) cJTAG

TIF>s

Specify target interface speed [kHz]. <Default>: 4000 kHz

Speed>

Device "NRF5340_XXAA_APP" selected.

Connecting to target via SWD

ConfigTargetSettings() start

ConfigTargetSettings() end - Took 13us

InitTarget() start

InitTarget() end - Took 2.10ms

Found SW-DP with ID 0x********

DPIDR: 0x6BA22677

CoreSight SoC-400 or earlier

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set, ADDR: 0x00000000)

AP[1]: AHB-AP (IDR: Not set, ADDR: 0x00000000)

AP[2]: MEM-AP (IDR: Not set, ADDR: 0x00000000)

AP[3]: MEM-AP (IDR: Not set, ADDR: 0x00000000)

AP[0]: Core found

AP[0]: AHB-AP ROM base: 0xE20FE200

CPUID register: 0x430FD216. Implementer code: 0x43 (???)

Feature set: Mainline

Cache: No cache

Found Cortex-M33 r0p6, Little endian.

FPUnit: 8 code (BP) slots and 2 literal slots

Security extension: implemented

Secure debug: enabled

CoreSight components:

ROMTbl[0] @ E20FE200

Memory zones:

Zone: "Default" Description: Default access mode

Cortex-M33 identified.

I tried changing the TRef to 3000 but it didnt' work:Connecting to target via SWD

ConfigTargetSettings() start

ConfigTargetSettings() end - Took 11us

InitTarget() start

InitTarget() end - Took 101ms

Failed to attach to CPU. Trying connect under reset.

Found SW-DP with ID 0xFBB03477

SWD speed too high. Reduced from 4000 kHz to 2700 kHz for stability

Failed to power up DAP

ConfigTargetSettings() start

ConfigTargetSettings() end - Took 7us

InitTarget() start

InitTarget() end - Took 2.27ms

Failed to attach to CPU. Trying connect under reset.

Found SW-DP with ID 0x******

SWD speed too high. Reduced from 2687 kHz to 1813 kHz for stability

Failed to power up DAP

Error occurred: Could not connect to the target device.

For troubleshooting steps visit: https://wiki.segger.com/J-Link_Troubleshooting

When I go back to 3300 I can connect but still face the [error] [ nRF53] - Failed while erasing device. -220: NVMC controller never gets ready. error.

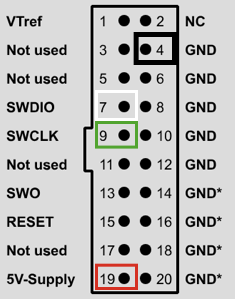

I'm using these pins on the Segger, which have been working for me up until this point:

I tried a reset using jlinkexe but got this:

J-Link>reset

Reset delay: 0 ms

Reset type: NORMAL (https://wiki.segger.com/J-Link_Reset_Strategies)

Reset: ARMv8M core with Security Extension enabled detected. Switch to secure domain.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via AIRCR.SYSRESETREQ.

Reset: S_RESET_ST never gets cleared. CPU seems to be kept in reset forever.

Reset: Using fallback: Reset pin.

Reset: Halt core after reset via DEMCR.VC_CORERESET.

Reset: Reset device via reset pin