Hi all,

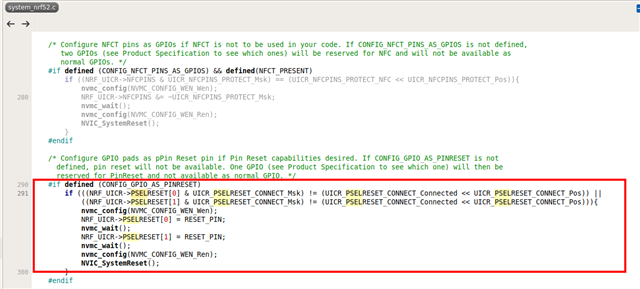

I'm working with the nRF52805 (QFN16) and was curious if the nRESET pin (P0.21) can be disabled via the UICR->PSELRESET[n] mechanism, as is possible on other nRF52 chips like the 52832.

After reviewing the nRF52805 PS v1.4 and Nordic’s online documentation (including this UICR page), I saw PSELRESET[0] and PSELRESET[1] described, including the CONNECT bit (bit 31) to disable the reset function.

-

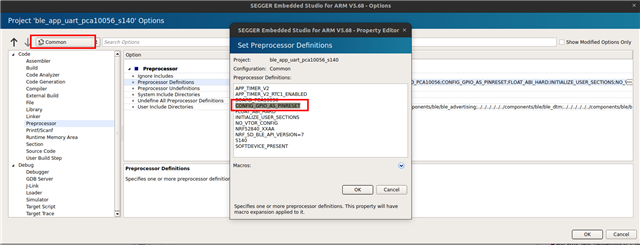

Used a debugger (J-Link + SES) to write the following:

NRF_UICR->PSELRESET[0] = (21 << 0) | (1UL << 31); // P0.21, disconnect NRF_UICR->PSELRESET[1] = (21 << 0) | (1UL << 31); -

Reset the MCU (

NVIC_SystemReset()). -

After reboot, printed the UICR values:

UICR->PSELRESET[0] = 0x00000015 UICR->PSELRESET[1] = 0x00000015(Expected

0x80000015if the disconnect bit was honored.) -

Tried configuring P0.21 as a GPIO and driving it low to light an LED.

-

The values were written without the

CONNECTbit sticking (bit 31 stayed cleared). -

The pin still behaves as a hardware reset input.

-

Any attempt to drive it low is still reading high — P0.21 is not usable as GPIO.

-

Meanwhile, other GPIOs (e.g. P0.04) behave normally.

TL;DR:

Although PSELRESET[n] is listed in nRF52805 documentation and accessible via firmware, the disconnect bit is not honored, and P0.21 always functions as nRESET.

-

Is this expected behavior, and should we consider the

PSELRESETfeature non-functional on the nRF52805 even in Rev 1.4? -

If so, could the docs be clarified to explicitly note that reset remapping is not supported on this part, despite the register existing?

Thanks, Bill!