How to change the parity bit on UART on NRF54L15?

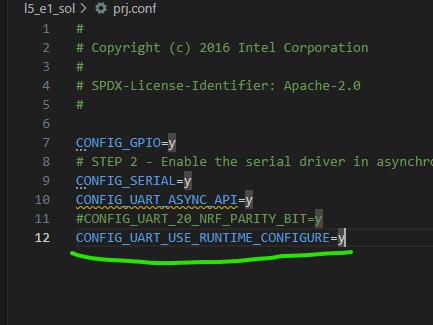

prj.conf includes:

CONFIG_SERIAL=y

CONFIG_UART_20_NRF_PARITY_BIT=y

DT overlay includes:

&uart20 {

parity = "even";

};

Also tried:

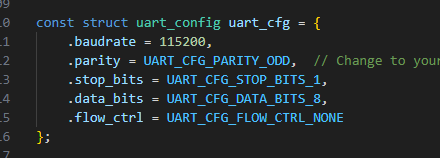

const struct uart_config uart_cfg = {

.baudrate = 115200,

.parity = UART_CFG_PARITY_EVEN,

.stop_bits = UART_CFG_STOP_BITS_1,

.data_bits = UART_CFG_DATA_BITS_8,

.flow_ctrl = UART_CFG_FLOW_CTRL_NONE

};

Then..

while(!device_is_ready(uart_dev));

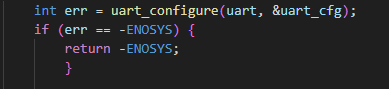

int err = uart_configure(uart_dev, &uart_cfg);

while(err == -ENOSYS);

..but err = -134 (-ENOSUP?)

Using Polling:

//Test 1

//Check for UART traffic

unsigned char uartRxBuff[20];

uartRxBuff[0] = 0;

int n = uart_poll_in(uart_dev, &uartRxBuff[0]);

if(uartRxBuff[0] != 0)

//if(uartRxBuff[0] == 0x79)

{

uartRxBuff[0] = 0x9f;

uart_poll_out(uart_dev, uartRxBuff[0]);

}

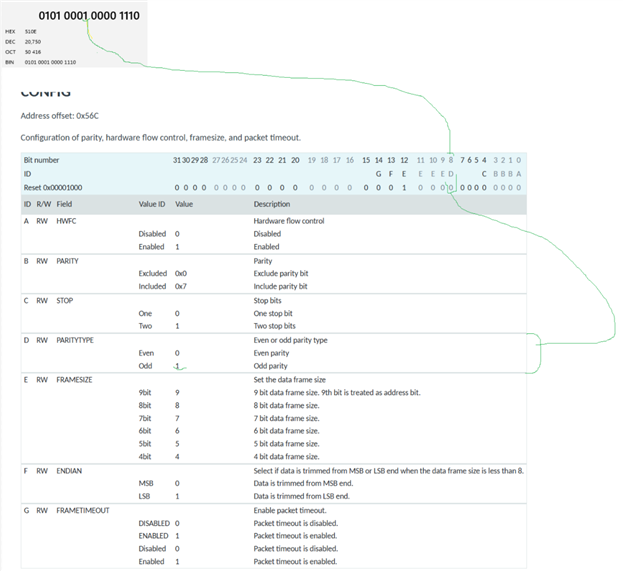

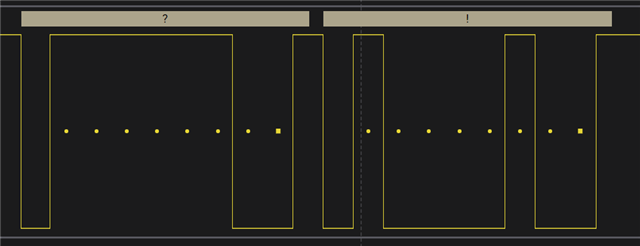

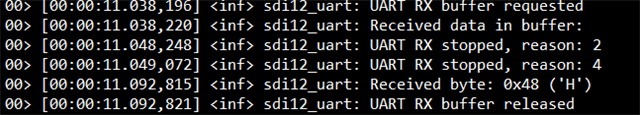

With Even parity on the other UART device it receives: 0x1f, if I send 0x1f in above code the other device receives 0x9f! Same deal with data received by NRF54L15 - the MSBit is flipped. If I switch the other device to parity=NONE (test FW - the actual FW is fixed at EVEN parity) the data comes thru correctly.

I was also unable to change the default UART20 RX/TX pins with the overlay - maybe it's the same problem?? It seems the overlay is ignored regarding UART20.

Is changing parity supported? Is there some conflict with TF-M or logging? How to change parity? The 'other' device uses EVEN parity and it cannot be changed.

Thanks!