Hi All,

Anyone has experience in FRAM?

I have a project which need to integrate the FRAM CY15B108QN with nRF52840.

I got a weird result by using nRF silicone, but can communicate perfectly using other sillicone (ESP32).

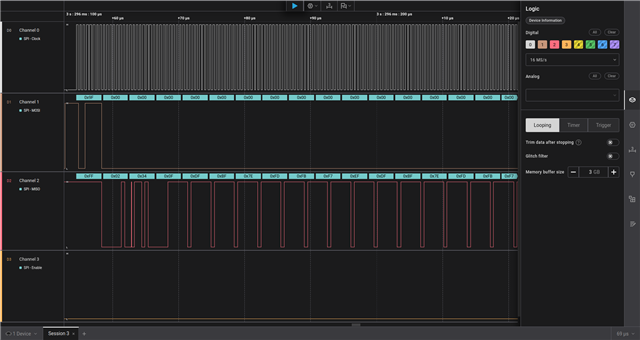

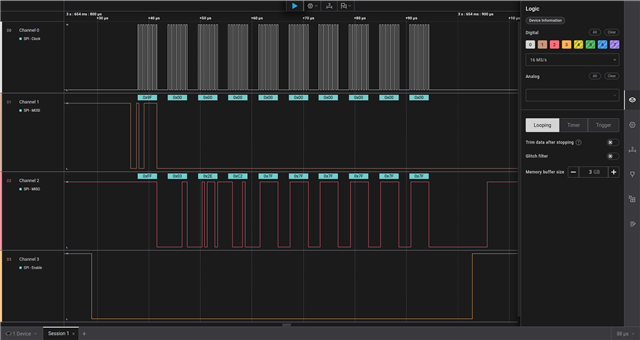

(1) (2)

(2)

(1) result when use zephyr; (2) result when use ESP32

Both sending 0x9F but having different response. The ESP32 result is matched with documentation, the zephyr one is not matched but consistently resulting the same value.

I've tried:

1. using SPI mode 0 and 3

2. vary the frequency

3. manually control the CS line

4. byte by byte transfer

5. using SPI 1 and SPI 3

6. using EEPROM SPI API by modify the fujitsu,mb85rsxx

7. raw simple SPI transaction

8. using SPI and SPIM

All have output the same result.

Appreciate your help.

Thanks