I want to try the tdm function on the nrf54lm20 dk.

But i have encountered problem in the first step.

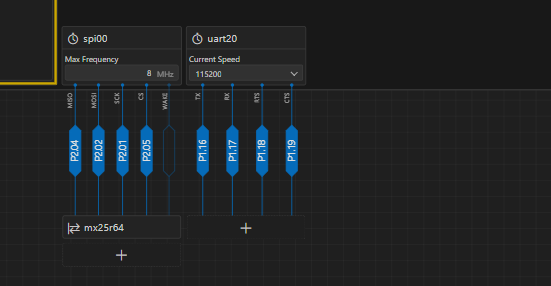

I do not know how to add the tdm port and assign the pin.

Whin i enable the tdm in the device tree, there is nothin in this page.

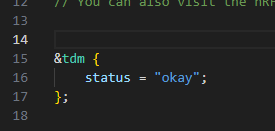

only this code generated in the overlay files

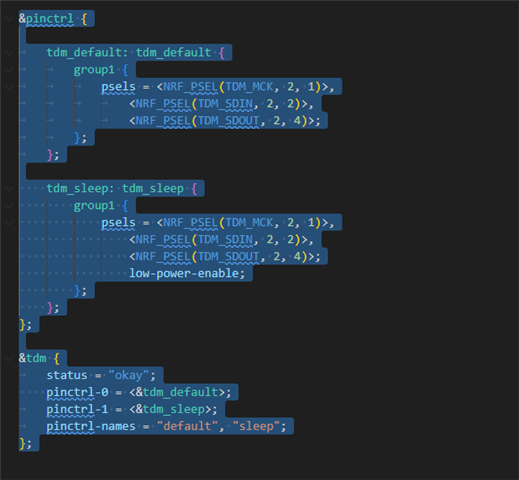

I try to assign the pin:

But seems invalid...

Can you help me to pass the first step?

Thank you very much!