Greetings,

We want to use the MCK of the I2S module as a clock output for an external device. For that, we need a freuqency of around 4,096MHz.

ACLK originates from the 32MHz HFXO, and can be set to 12.288MHz (nrf5340_PS 4.11.1.3 Audio oscillator).

The master clock generator can now divide ACLK by 3 to arrive at 4,096MHz.

Devicetree overlay:

i2s_rx: &i2s0 {

status = "okay";

clock-source = "ACLK";

pinctrl-0 = <&i2s0_default_alt>;

pinctrl-names = "default";

};

&clock {

hfclkaudio-frequency = <12288000>;

};

Using the Zephyr API, the I2S registers can not be configured directly, but it works with a small workaround:

/* --- I2S Parameter --- */ #define SAMPLE_RATE_HZ 128000u #define WORD_SIZE_BITS 16u #define CHANNELS 2u

With this, I set the bit-clock to 4,096MHz. MCK should be the same.

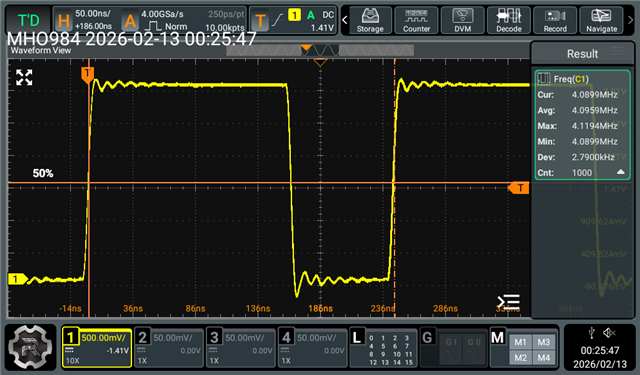

Now, measuring MCK (or SCK) with the oscilloscope shows, that we get an unstable frequency between 4,125MHz and 4,135MHz.

The main issue for us is not that the frequency is slightly off, but that it appears to be unstable.

I wonder how that can be. The quarz frequency should be reliable, and the Master clock generator just divides the frequency by 3.

So I would suspect the generation of ACLK to be unstable.

How exactly is ACLK created? Or do you have any idea what could cause this behavior, or whether there is anything incorrect in my setup?

Thanks a lot :)