I know this is somewhat "how long is a piece of string". I'm happy for guidance rather than solid numbers:

I'm trying to spec a "keep alive" circuit for an nRF51822 project. The general principle is there is an LDO (with enable pin) that is first activated by a user pushbutton. Next, as fast as possible, the nRF51822 turns-on (now that it has power) and switches on a GPIO to keep the LDO enable pin high (therefore keeping the LDO on). This means the nRF can turn everything off by setting the enable pin to low.

To keep the enable line high during the time between the button being pressed & released, and the nRF51822 to wake-up, I'm just using a capacitor and resistor specified with the right discharge duration. So the time for RC-discharge to minimum enable-pin voltage needs to be a bit longer than the power-on time for the nRF51822.

I've looked at the product specification and especially at this related question here: devzone.nordicsemi.com/.../

I know that the practical start-up time (from power-input to GPIO-output) depends on the input voltage, I'm using 3.3V which should give pretty fast start-up (~2ms according to linked question).

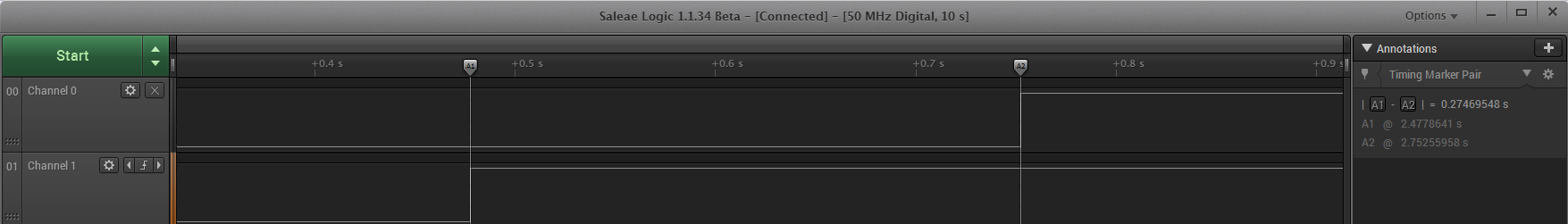

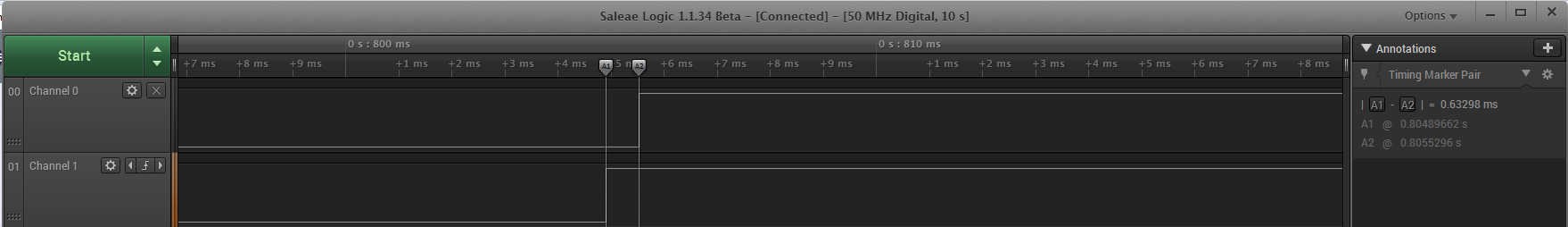

But... Using the nRF51-DK dev. board to prototype this I see with my oscilloscope that the practical start-up time is more like 350-400ms... It's dramatically larger than what I was expecting... Obviously this start-up time includes LDO start-up, but that is ~50uS according to my scope.

So, my main question(s):

- Does the nRF51-DK take much longer to start than a raw/lone nRF51822 module?

- Approximately what start-up times could I expect with a real nRF51822 module? (Are values in the product spec. & the related question realistic for the power-on->GPIO-on start-up time I'm describing?)

My circuit is very flexible and I can manage even these large start-up times, but reducing it to product spec. values would be very useful to avoid a big capacitor.

Sorry for the long question, lots of detail. Any help/advice is appreciated.