Hi,

can you please to provide a more information regard power up sequence?

for example:

we would like to use DC2DC (instead LDO) with CR2032 battery.

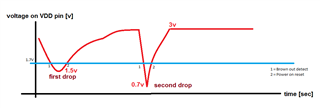

the PCB have nRF52832 and battery holder, while I put in the battery to battery holder there is chanse for a voltages drop for example :

once VDD supplied by "high enough voltage" then boot loader start with FW upload from internal FLASH, if at the time that FW uploaded from internal FLASH happened some drop voltage to X and time of drop is Y.

please explain :

1. what the time and stablle value of voltage is mandatory for start process of FW upload from internal FLASH to RAM ? (I think that the FW run on the RAM not on the FLASH)

2. what happened while FW uploaded from internal FLASH to RAM and some drop occured, so bootloader will be restart uploading process ?

3. bootloader have some CRC checking about uploaded FW?