Hi

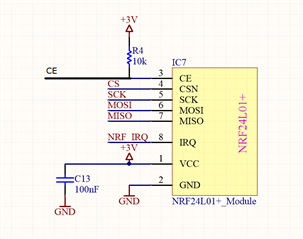

I try to communicate with my NRF24L01+.

For this, i have connected a mikrocontroller to my Module.

Actually i am using a small piece of code, which allows me to send SPI Commands mannualy from the serial interface to the module.

My Actual procedure is:

- PowerUp

- Set CS high

- Set CS low

- Send 0x0A (To Read the Address of Pipe 3)

- Send five times 0xFF to get the answer

- Set CS high

here comes a delay caused by the human who is entering the commands to the console ;)

- Set CS low

- Send 0x0A (To Read the Address of Pipe 3)

- Send five times 0xFF to get the answer

- Set CS high

The problem is now, that i get the correct answer during the first procedure after power up.

In the second procedure, i get only 0x00 except of the STATUS Register. This changes from 0x0E to 0x1C.

I have attached an logicanalyzer directly to the modules pins.

The result is attached.

The Power is clean and come from an LDO, buffered with 100nF and 4.7uF MLCC directly at the module.

All Voltages are ~3.28V. Also for a high Level. And a low-level is around ~0.08V

I dont have any idea how to get further.

I would be very happy if anyone could help me with this problem.

Thank you

Here Are the Pictures:

First Command after PowerUp:

Second Command: