Hello,

While I was making SPIS part, I got several issues.

I am using STM32L151CB for SPI Master and nRF51822 for SPI Slave. It seems many people had issues with SPIS.

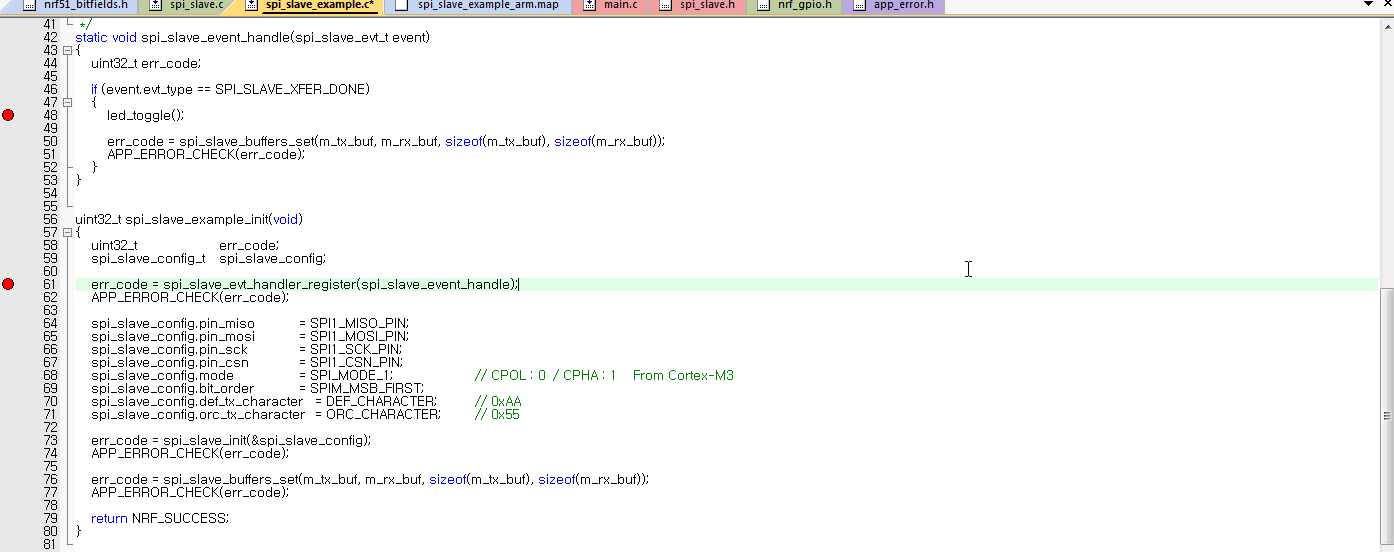

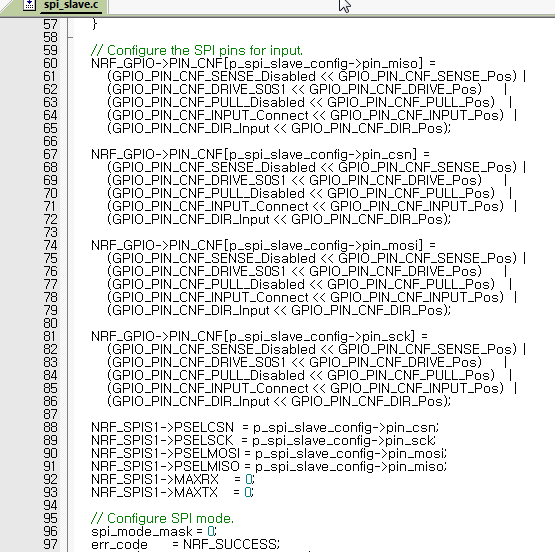

SPIS Setting Code is here.

/**************************************************************************************************/

err_code = spi_slave_evt_handler_register(spi_slave_event_handle);

APP_ERROR_CHECK(err_code);

spi_slave_config.pin_miso = SPI1_MISO_PIN;

spi_slave_config.pin_mosi = SPI1_MOSI_PIN;

spi_slave_config.pin_sck = SPI1_SCK_PIN;

spi_slave_config.pin_csn = SPI1_CSN_PIN;

spi_slave_config.mode = SPI_MODE_1; // CPOL : 0 / CPHA : 1 From Cortex-M3

spi_slave_config.bit_order = SPIM_MSB_FIRST;

spi_slave_config.def_tx_character = DEF_CHARACTER; // 0xAA

spi_slave_config.orc_tx_character = ORC_CHARACTER; // 0x55

err_code = spi_slave_init(&spi_slave_config);

APP_ERROR_CHECK(err_code);

err_code = spi_slave_buffers_set(m_tx_buf, m_rx_buf, sizeof(m_tx_buf), sizeof(m_rx_buf));

APP_ERROR_CHECK(err_code);

return NRF_SUCCESS;

/**************************************************************************************************/

STM32L151 is using CPOL as 0 and CPHA as 0, so I set SPI_MODE as SPI_MODE_1, and it uses MSB_First.

Is there any problem?

- Are initial values of MAXRX and MAXTX registers right values?

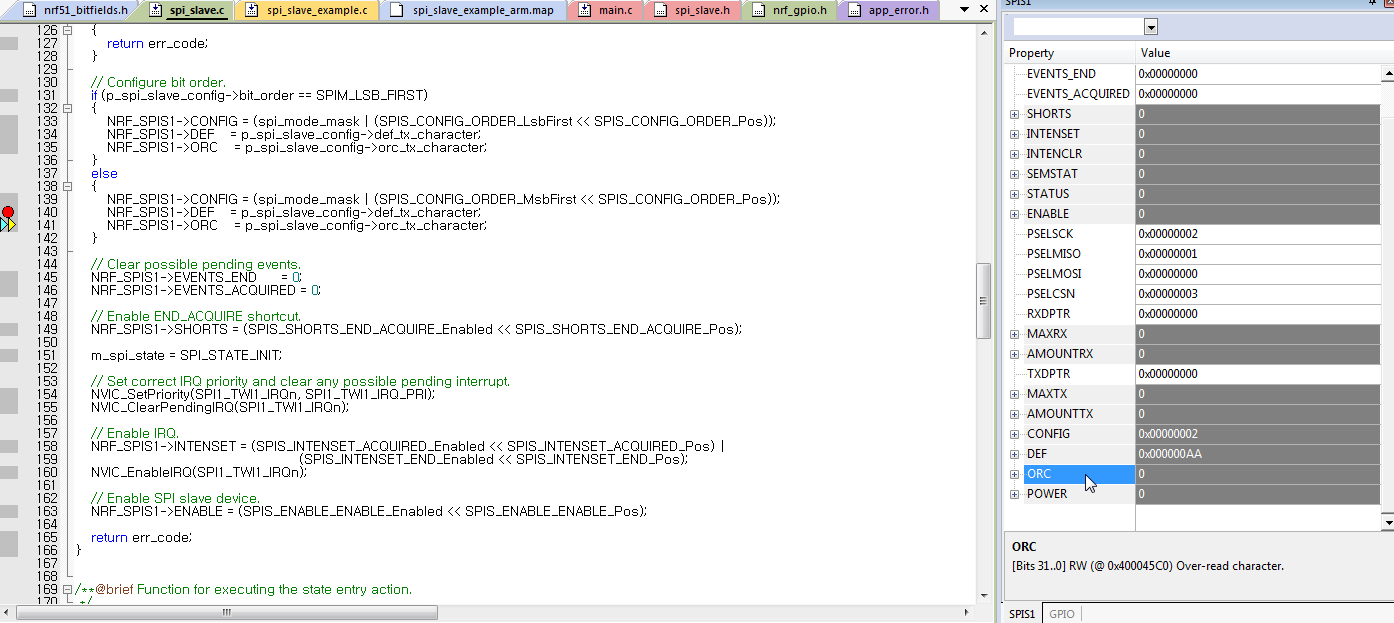

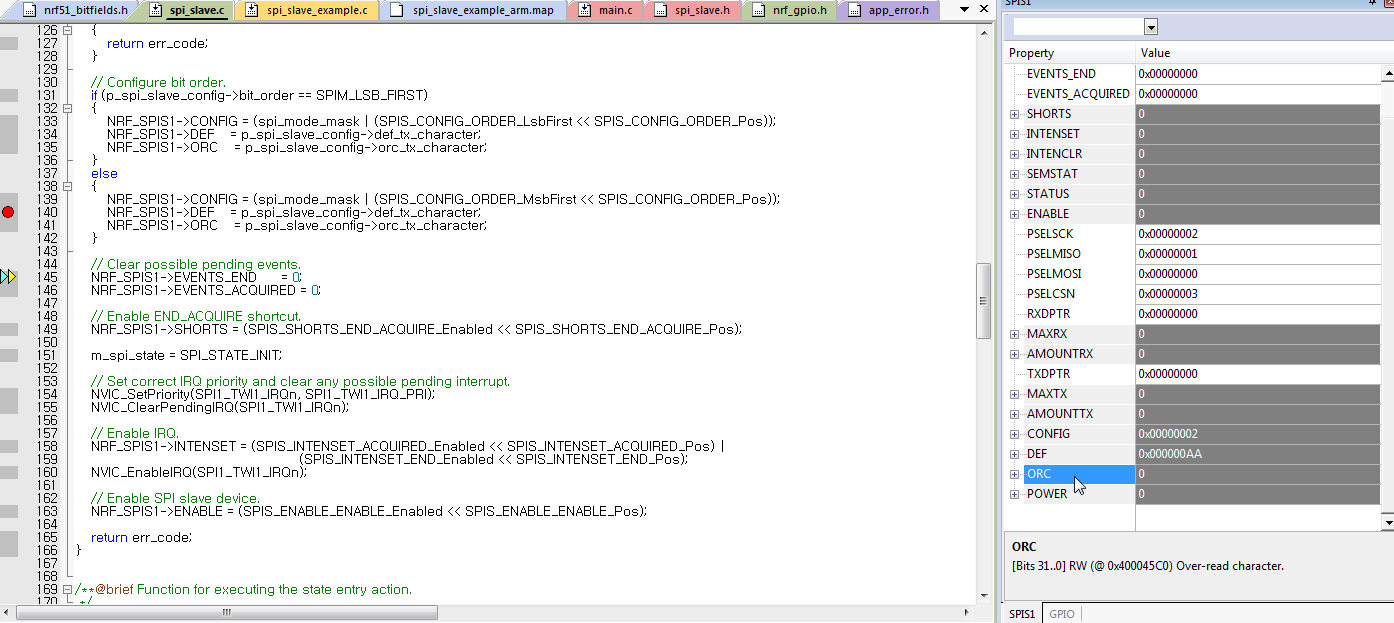

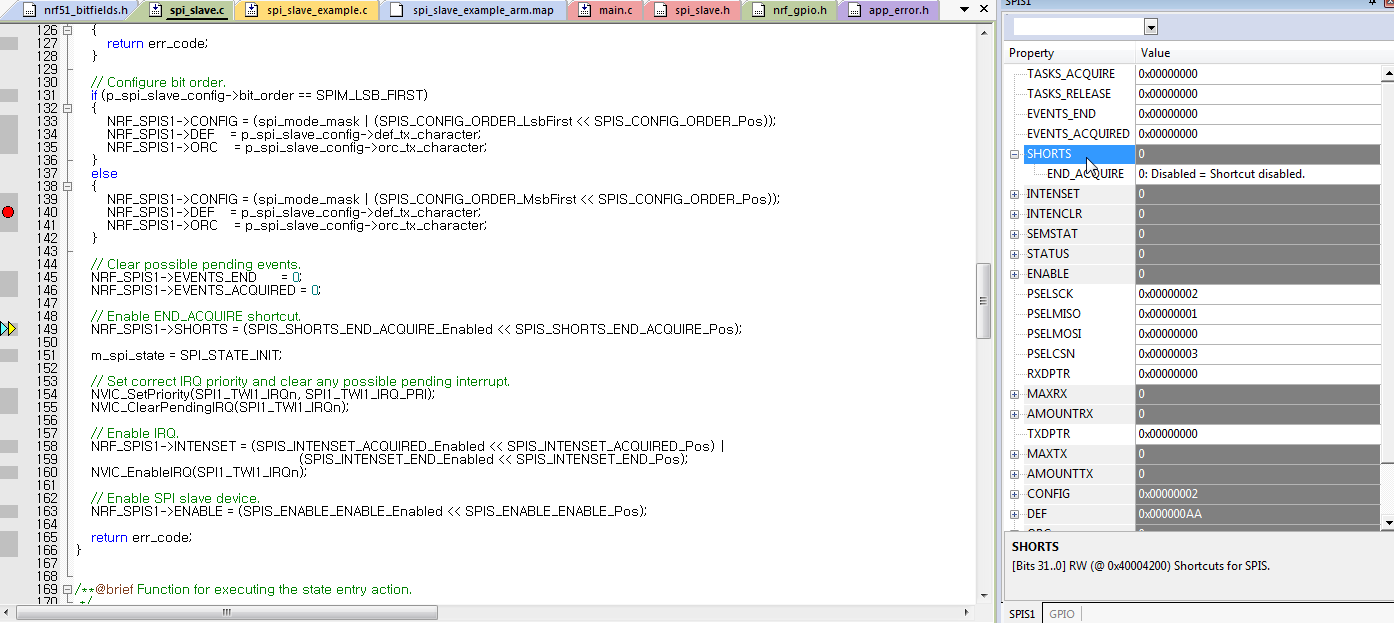

- After setting NRF_SPIS1->DEF register, I found something strange on register values.

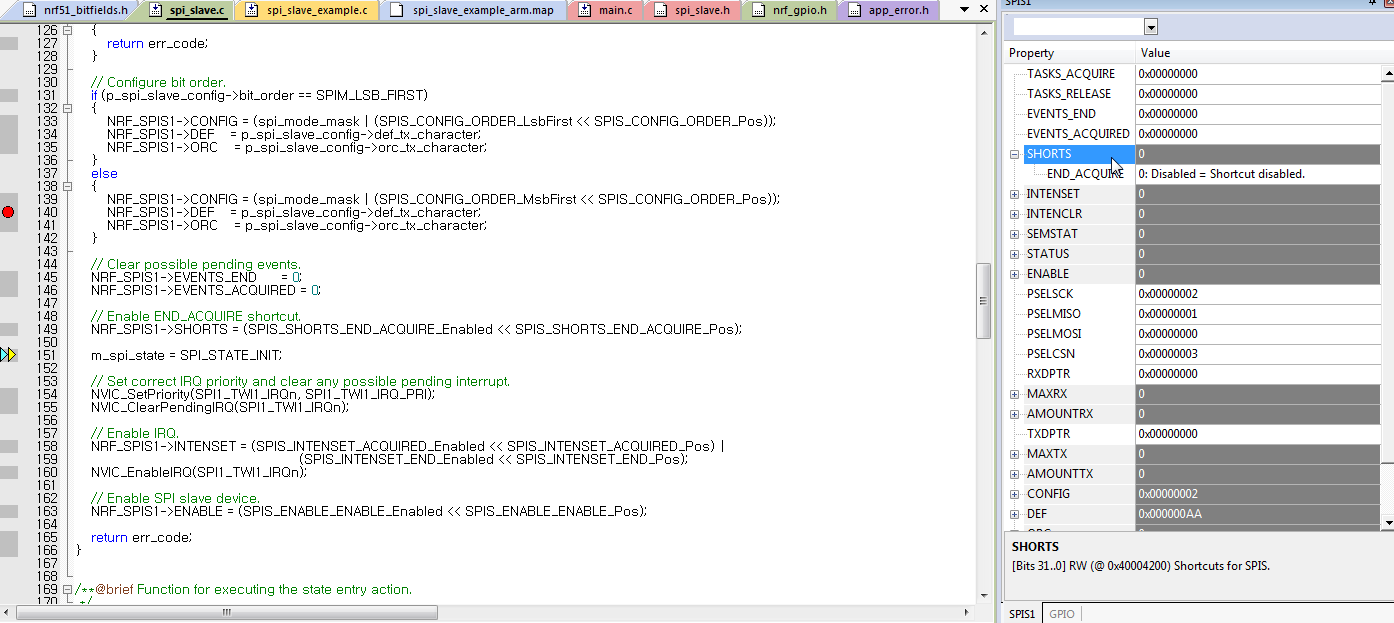

2.1 NRF_SPIS1->ORC = 0x55 doesn't work at all. See below 2 capture images.

2.2 NRF_SPIS1->SHORTS register is not able to change. See below 2 capture images. Of course, I checked SPIS_SHORTS_END_ACQUIRE_Enabled is 0x01.

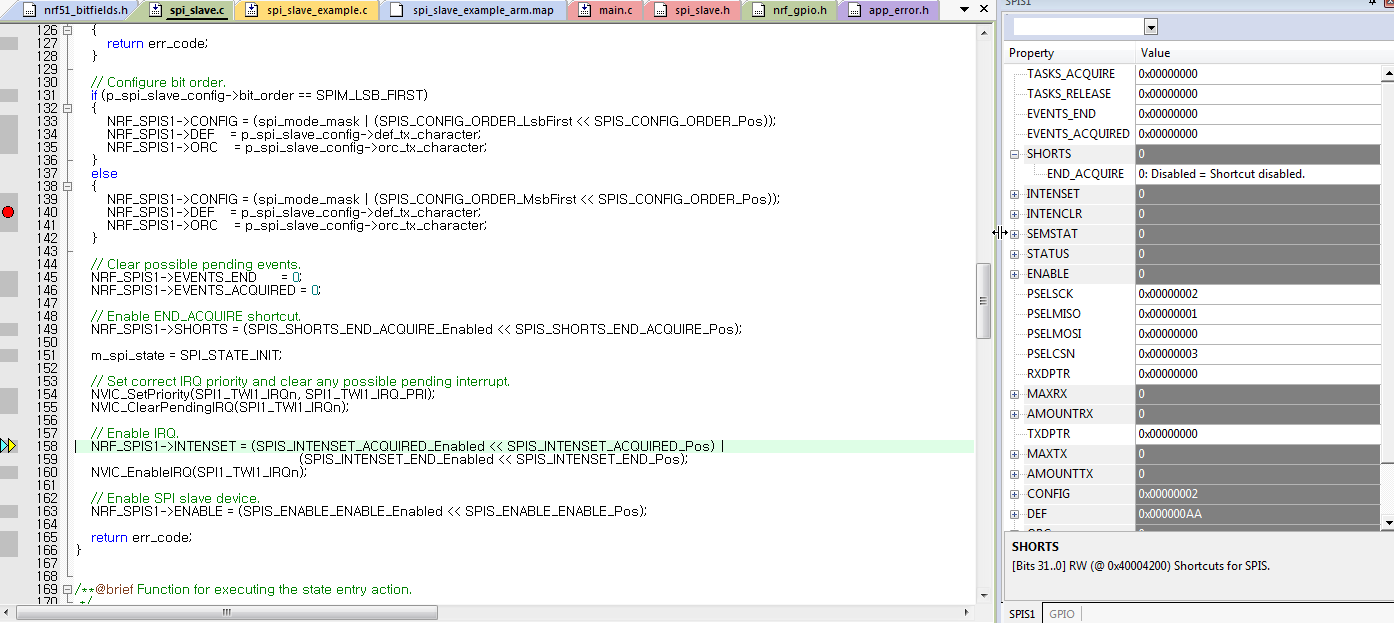

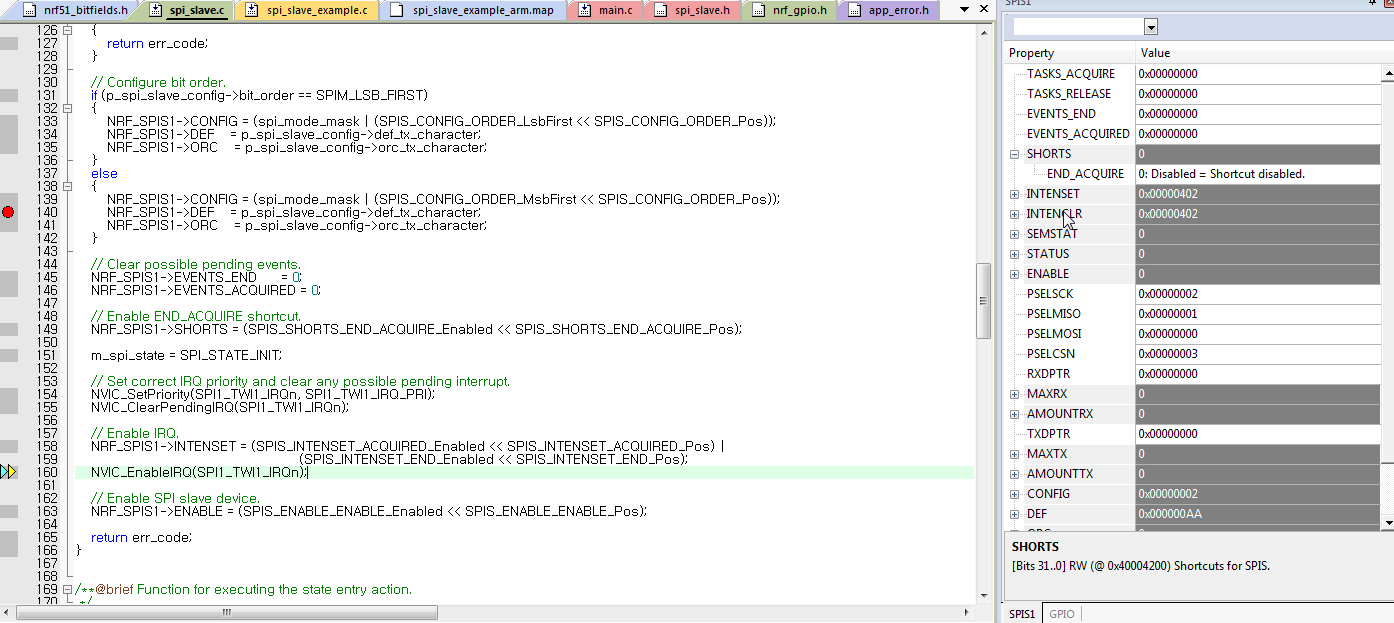

- NRF_SPIS1->INTENCLR is set automatically when NRF_SPIS1->INTENSET is set. See below 2 images.

Because my code can't jump into spi_slave_event_handle(SPIS handler), so I have been struggling with codes, and I want to know whether I made any mistakes for SPIS setting.

Thank you for reading, and I hope to see your answer. Thanks.

Ryan