Hi all !

I have been working on an nRF51822 based board for a little while, the ten 1st prototypes worked well so we asked our factory to make 20 other with the same design files.

Even after a hard week of debugging (and PAN doc + forum investigation), we still struggle to find why we get can not connect to target.

The CPU revision is now a G0 and the 1st batch had a C0 but it should not be a problem. Anyway, to demonstrate this problem, we made a couple of videos / pictures to compare the faulty batch to the old one, which works.

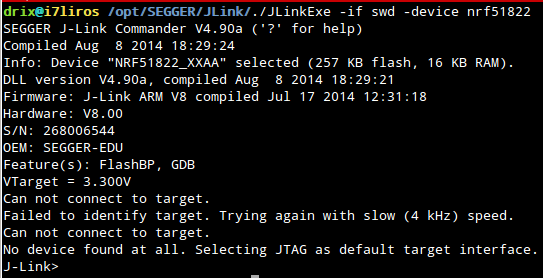

- We connect the probe and launch

JLinkExe -if SWD -device nRF51822to see if the CPU is detected, but it works on the old boards, not on the new one:

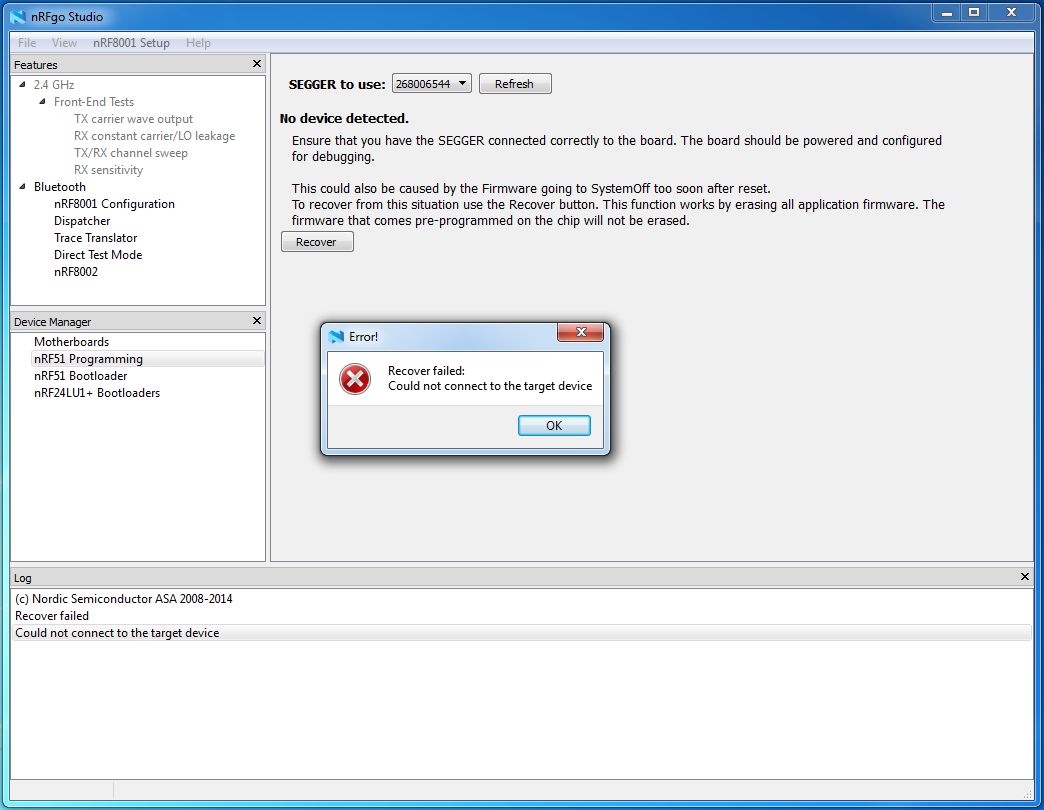

- We also tried to recover the CPU with nRF go studio but it failed too:

- The power supply could be a problem so we checked it and we compared all the decoupling capacitors, no problem there.

EDIT: we also tried to power the board with 3.3V but it didn't help (thanks a lot Nguyen Hoan Hoang for the suggestion):

There is a difference in the DEC1 pin voltage between C0 and G0 revisions though, but we compared with another working G0 board and it's coherent:

- The PCBs are beautiful and cleanly soldered so we don't think that it can be the problem, but we might be wrong.

EDIT2: We've also investigated the way the reset is done but we didn't find much that could help. Is it possible without a jlink connection ?

Would anyone have any suggestion on further investigations to understand what's wrong with these boards ?

Thanks a lot for your help !

Cedric ;)

PS: if the design can be helpful, it's open source and available online: portfolio.honnet.eu/twi