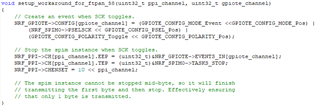

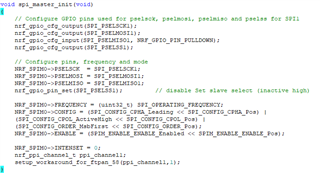

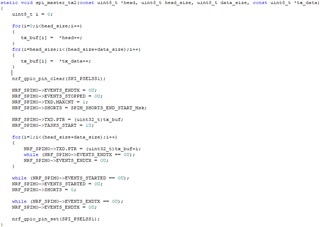

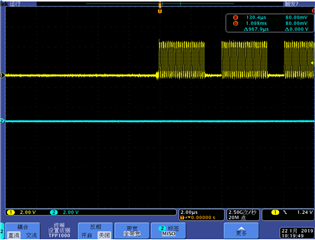

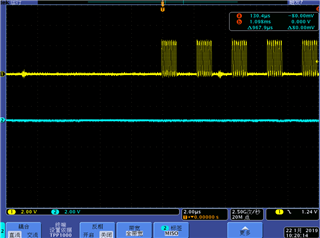

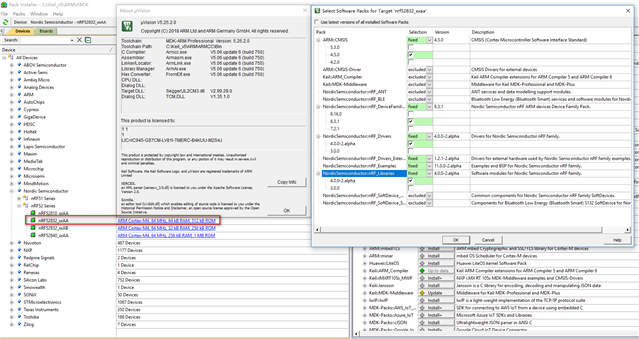

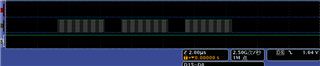

I use nrf52832 SPIM, and I want there are gaps between every 8clock, so I set NRF_SPIM0->TXD.MAXCNT = 1; NRF_SPIM0->RXD.MAXCNT = 1; ,But there is alway more clock than I want,(I want to write 8clock, but there are 16clock), then the nordic engineer tell me to use PPI(setup_workaround_for_ftpan_58). now, the SPI work well , but I find another question, I must put P0.30 as output pin,and there is gaps between every 8clock, If I didn't config P0.30, there is not gaps between every 8clock, just like bellow,is that right?

I asked the quetion in https://devzone.nordicsemi.com/f/nordic-q-a/40522/nrf52832-spi-psel-sck-timing, but there is no reply.There are more details in the link.