SDK v15.2.0 using peripheral spi example. Windows 8.1, uploading to nRF52 DK.

/**

* Copyright (c) 2015 - 2018, Nordic Semiconductor ASA

*

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without modification,

* are permitted provided that the following conditions are met:

*

* 1. Redistributions of source code must retain the above copyright notice, this

* list of conditions and the following disclaimer.

*

* 2. Redistributions in binary form, except as embedded into a Nordic

* Semiconductor ASA integrated circuit in a product or a software update for

* such product, must reproduce the above copyright notice, this list of

* conditions and the following disclaimer in the documentation and/or other

* materials provided with the distribution.

*

* 3. Neither the name of Nordic Semiconductor ASA nor the names of its

* contributors may be used to endorse or promote products derived from this

* software without specific prior written permission.

*

* 4. This software, with or without modification, must only be used with a

* Nordic Semiconductor ASA integrated circuit.

*

* 5. Any software provided in binary form under this license must not be reverse

* engineered, decompiled, modified and/or disassembled.

*

* THIS SOFTWARE IS PROVIDED BY NORDIC SEMICONDUCTOR ASA "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY, NONINFRINGEMENT, AND FITNESS FOR A PARTICULAR PURPOSE ARE

* DISCLAIMED. IN NO EVENT SHALL NORDIC SEMICONDUCTOR ASA OR CONTRIBUTORS BE

* LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR

* CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE

* GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION)

* HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT

* LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT

* OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

#include "bma2x2.h"

#include "nrf_drv_spi.h"

#include "app_util_platform.h"

#include "nrf_delay.h"

#include "boards.h"

#include "app_error.h"

#include <string.h>

#include "nrf_log.h"

#include "nrf_log_ctrl.h"

#include "nrf_log_default_backends.h"

#define SPI_INSTANCE 0 /**< SPI instance index. */

static const nrf_drv_spi_t spi = NRF_DRV_SPI_INSTANCE(SPI_INSTANCE); /**< SPI instance. */

static volatile bool spi_xfer_done; /**< Flag used to indicate that SPI instance completed the transfer. */

#define BMA2x2_SPI_BUS_WRITE_CONTROL_BYTE 0x7F

#define BMA2x2_SPI_BUS_READ_CONTROL_BYTE 0x80

#define SPI_BUFFER_LEN 5

static uint8_t m_rx_buf[SPI_BUFFER_LEN]; /**< RX buffer. */

#define BMA_ERROR_CHECK(ERR_CODE) { APP_ERROR_CHECK((ret_code_t) ERR_CODE); }

/**

* @brief SPI user event handler.

* @param event

*/

void spi_event_handler(nrf_drv_spi_evt_t const * p_event,

void * p_context)

{

spi_xfer_done = true;

NRF_LOG_INFO("Transfer completed.");

if (m_rx_buf[0] != 0)

{

NRF_LOG_INFO(" Received: %x", m_rx_buf[0]);

}

}

s8 bma_spi_write(u8 dev_addr, u8 reg_addr, u8 *reg_data, u8 cnt)

{

s8 error = NO_ERROR;

uint8_t tx_buf[cnt+1];

// place write bit + address in first byte

tx_buf[0] = (reg_addr++) & ~BMA2x2_SPI_BUS_WRITE_CONTROL_BYTE;

for (uint8_t string_pos = 1; string_pos < cnt+1; string_pos++)

{

// place data in second byte

tx_buf[string_pos] = *(reg_data + string_pos - 1);

}

spi_xfer_done = false;

error = (s8) nrf_drv_spi_transfer(&spi, tx_buf, cnt+1, NULL, 0);

BMA_ERROR_CHECK(error);

return error;

}

s8 bma_spi_read(u8 dev_addr, u8 reg_addr, u8 *reg_data, u8 cnt)

{

s8 error = NO_ERROR;

uint8_t tx_buf[1] = {reg_addr|BMA2x2_SPI_BUS_READ_CONTROL_BYTE};

spi_xfer_done = false;

error = (s8) nrf_drv_spi_transfer(&spi, tx_buf, 1, reg_data, cnt);

BMA_ERROR_CHECK(error);

return error;

}

void spi_delay(u32 millis_time)

{

nrf_delay_ms(millis_time);

}

int main(void)

{

APP_ERROR_CHECK(NRF_LOG_INIT(NULL));

NRF_LOG_DEFAULT_BACKENDS_INIT();

nrf_drv_spi_config_t spi_config = NRF_DRV_SPI_DEFAULT_CONFIG;

spi_config.ss_pin = SPI_SS_PIN; //29 -> 17

spi_config.miso_pin = SPI_MISO_PIN; //28 -> 8

spi_config.mosi_pin = SPI_MOSI_PIN; //4 -> 6

spi_config.sck_pin = SPI_SCK_PIN; //3 -> 15

spi_config.mode = NRF_DRV_SPI_MODE_3;

spi_config.bit_order = NRF_SPI_BIT_ORDER_MSB_FIRST;

APP_ERROR_CHECK(nrf_drv_spi_init(&spi, &spi_config, spi_event_handler, NULL));

NRF_LOG_INFO("SPI hardware initialised.");

struct bma2x2_t bma2x2;

bma2x2.chip_id = BMA2x2_INIT_VALUE;

bma2x2.bus_write = &bma_spi_write;

bma2x2.bus_read = &bma_spi_read;

bma2x2.dev_addr = 102; // Random value. No chip select mechanism in place

bma2x2.delay_msec = &spi_delay;

BMA_ERROR_CHECK(bma2x2_init(&bma2x2));

if (bma2x2.chip_id == 0xFD)

{

NRF_LOG_INFO("BMA API initialised.");

}

else

{

NRF_LOG_INFO("BMA chip id: %x", bma2x2.chip_id);

}

while (1)

{

u8 m_rx[1] = {0xFF};

bma_spi_read(0, 0, m_rx, sizeof(m_rx));

NRF_LOG_INFO("m_rx: %x", m_rx[0]);

nrf_delay_us(2);

bma_spi_read(0, 0, m_rx, sizeof(m_rx));

NRF_LOG_INFO("m_rx_2: %x", m_rx[0]);

while (!spi_xfer_done)

{

__WFE();

}

NRF_LOG_FLUSH();

nrf_delay_ms(1000);

}

}

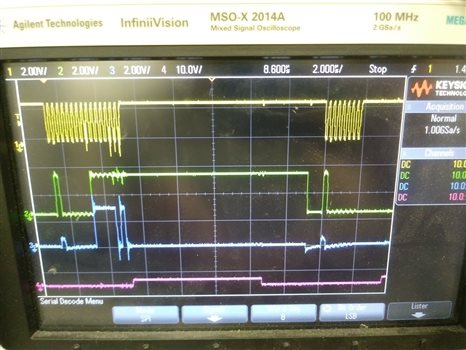

In my while loop I use bma_spi_read() twice with a small delay in between. The first call includes 16 clock pulses as expected but the second only includes 8. I do not know why.