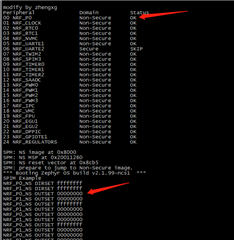

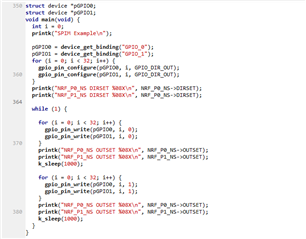

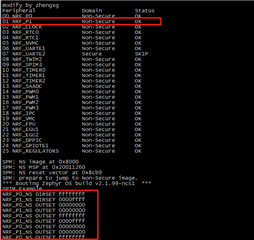

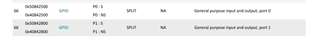

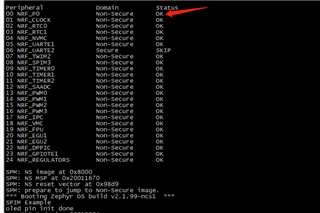

I can control GPIO P0,but can't control P1, when I load project with nrf5340_dk_nrf5340_cpuappns configuration.

If I load project with nrf5340_dk_nrf5340_cpuapp configuration, I can control both P0 and P1.

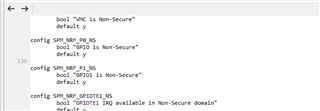

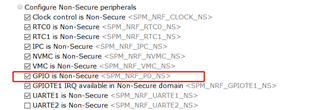

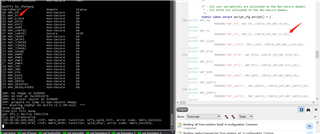

Why there is no P1 in nrf5340_dk_nrf5340_cpuappns spm configuration?

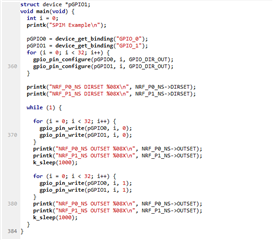

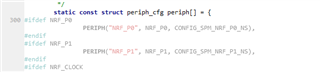

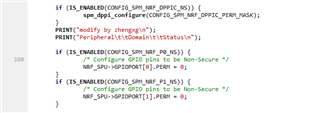

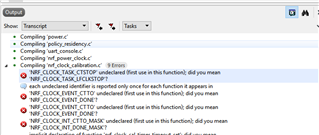

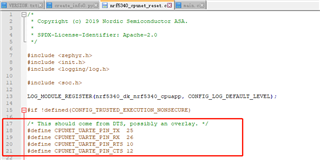

I tried to add P1 config manually in spm.c and Kconfig, but I still couldn't control P1.

The source code is based on ncs v1.2.0,and is a continuation of the following problem https://devzone.nordicsemi.com/f/nordic-q-a/58966/is-there-any-sample-for-spi-based-on-nrf5340