I'm using the SPI Manager to send large transfers of data to a graphics controller. What I see is that, once a single byte is transferred, the CS line will continue to pulse on it's own every 1ms. It doesn't start until after a first transaction is complete.

Here's a shot of that first single byte:

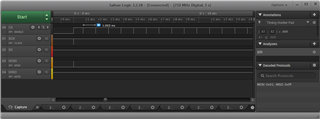

And right after that the regular 1ms CS pulses start:

They keep going until the system is reset.

I've reduced by configuration down to a simple state for debugging the issue:

nrf_drv_spi_config_t const m_disp_ILI9341_spi_config =

{

.sck_pin = SPI_SCK_PIN,

.mosi_pin = SPI_MOSI_PIN,

.miso_pin = SPI_MISO_PIN,

.ss_pin = DISP_CS, // NRF_GPIO_PIN_MAP(0,31)

.irq_priority = APP_IRQ_PRIORITY_LOWEST,

.orc = 0xFF,

.frequency = NRF_DRV_SPI_FREQ_8M,

.mode = NRF_DRV_SPI_MODE_3,

.bit_order = NRF_DRV_SPI_BIT_ORDER_MSB_FIRST

};

uint8_t ER_TFT020_1_CMD_TRANSFER_DATA[] = {0x00};

nrf_spi_mngr_transfer_t ER_TFT020_1_CMD_TRANSFER = NRF_SPI_MNGR_TRANSFER(ER_TFT020_1_CMD_TRANSFER_DATA, sizeof(ER_TFT020_1_CMD_TRANSFER_DATA), NULL, 0);

nrf_spi_mngr_transaction_t ER_TFT020_1_CMD_TRANSACTION =

{

.begin_callback = NULL,

.end_callback = NULL,

.p_user_data = NULL,

.p_transfers = &ER_TFT020_1_CMD_TRANSFER,

.number_of_transfers = 1,

.p_required_spi_cfg = &m_disp_ILI9341_spi_config

};

// Add a byte to the transfer buffer ER_TFT020_1_CMD_TRANSFER_DATA[0] = 0x01; // Schedule the transaction ret_val = spi0_master_sched_transaction(&ER_TFT020_1_CMD_TRANSACTION);

I've checked to make sure the pin isn't being used by other parts of the code. I've verified it doesn't start until that first byte is sent. There's no activity on the CS line before that. There are two other SPI chips in the system but they have seperate CS lines and their own nrf_drv_spi_config_t configuration structures. Is it possible the SPI Manager is periodically pulsing the CS line? If so, why and how to I turn it off?

Thanks in advance.

.