Hello

I would like use at least 2PPI channels to control a GPIO.

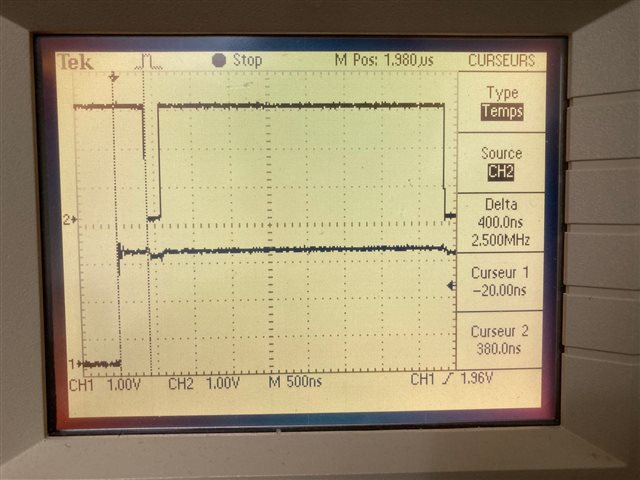

If PPI CH0&CH1 both setup, then GPIO_CTL just go high.

If PPI CH0 remarked, then GPIO_CTL go low

How to use 2ppi to control 1gpio?

The code as below

uint32_t PPI_evt_addr;

uint32_t PPI_task_addr;

nrf_ppi_channel_t ppi_channel;

/* PPI CHANNEL0 SETUP */

ppi_channel=NRF_PPI_CHANNEL0;

nrf_drv_gpiote_out_config_t config_1=GPIOTE_CONFIG_OUT_TASK_HIGH;

nrf_drv_gpiote_out_init(GPIO_CTL , &config_1);

nrf_drv_ppi_channel_alloc(&ppi_channel);

PPI_evt_addr = nrf_drv_timer_event_address_get(&TIMER1, NRF_TIMER_EVENT_COMPARE0);

PPI_task_addr = nrf_drv_gpiote_out_task_addr_get(GPIO_CTL);

nrf_drv_ppi_channel_assign(ppi_channel, PPI_evt_addr, PPI_task_addr);

nrf_drv_ppi_channel_enable(ppi_channel);

nrf_drv_gpiote_out_task_enable(GPIO_CTL);

/* PPI CHANNEL1 SETUP */

ppi_channel=NRF_PPI_CHANNEL1;

nrf_drv_gpiote_out_config_t config_0=GPIOTE_CONFIG_OUT_TASK_LOW;

nrf_drv_gpiote_out_init(GPIO_CTL , &config_0);

nrf_drv_ppi_channel_alloc(&ppi_channel);

PPI_evt_addr = nrf_drv_timer_event_address_get(&TIMER2, NRF_TIMER_EVENT_COMPARE0);

PPI_task_addr = nrf_drv_gpiote_out_task_addr_get(GPIO_CTL);

nrf_drv_ppi_channel_assign(ppi_channel, PPI_evt_addr, PPI_task_addr);

nrf_drv_ppi_channel_enable(ppi_channel);

nrf_drv_gpiote_out_task_enable(GPIO_CTL);