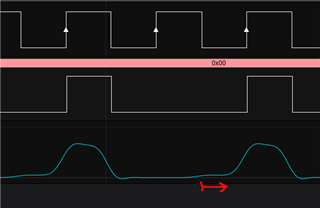

I've been observing a strange behaviour on the MOSI line using SPI2 in Mode 0(nRF52832) with connected ST7789 based display,

The data happens to be not available at the time of the sampling clock. This happens rarely, only in Mode 0 and only with the mentioned peripheral(ST7789).

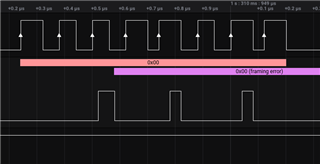

Using different display with ST7735, this behaviour is not visible:

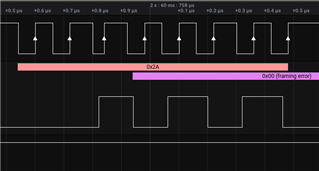

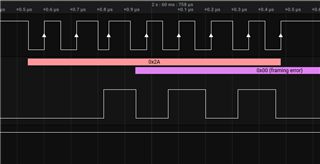

Logically this could be explained with some issues with the ST7789 hardware, but keeping in mind that the data pin is solely input(not a tri-state) and the the fact that this is not happening when Mode 3 is used, I am really confused what can be the reason.

Mode 3, ST7789(working fine):

The code used for both displays is the same(no board reprogramming, just plug and play), snapshot follows:

#include "nrf_drv_spi.h"

...

static const nrf_drv_spi_t spi = NRF_DRV_SPI_INSTANCE(2); /**< SPI instance. */

static volatile bool spi_xfer_done=1; /*< Flag used to indicate that SPI instance completed the transfer. */

...

void spi_event_handler(nrf_drv_spi_evt_t const * p_event, void * p_context)

{

spi_xfer_done = 1;

}

...

void SPI_Init(void){

nrf_drv_spi_config_t spi_config = NRF_DRV_SPI_DEFAULT_CONFIG;

spi_config.ss_pin = NRF_DRV_SPI_PIN_NOT_USED;

spi_config.miso_pin = NRF_DRV_SPI_PIN_NOT_USED;

spi_config.mosi_pin = TFT_MOSI; //p0.26

spi_config.sck_pin = TFT_MCLK; //p0.27

spi_config.frequency = NRF_DRV_SPI_FREQ_8M;

spi_config.mode = NRF_DRV_SPI_MODE_0; //NRF_DRV_SPI_MODE_3;

APP_ERROR_CHECK(nrf_drv_spi_init(&spi, &spi_config, spi_event_handler, NULL));

}

...

void SPI_Write(uint8_t * data){ //Single byte transfer

if(spi_xfer_done == 0){return;}

spi_xfer_done = 0;

APP_ERROR_CHECK(nrf_drv_spi_transfer(&spi, data, 1, m_rx_buf, 0));

while (!spi_xfer_done)

{

__WFE();

}

}

I already have a solution using Mode 3(1,1) but I am really curious if someone have experienced similar issue and what could be the possible cause.

I would appreciate any comments on this.

Kind regards,

Stefan