Hi Devzone:

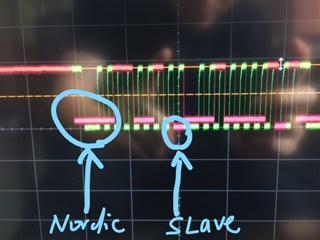

I am using P0.00 as SDA and P0.01 as SCL on nRF52833, And I got waveforms like below when I am doing I2C transactions:

the red waveform is SDA and the green waveform is SCL.

As shown in the picture the nordic chip doesn't pull the SDA line (red) all the way down to voltage zero when it's 0.

We already have 1.8V and a pull up resistor of 1.8K ohm on both pins.

I looked at twi config settings (nrf_drv_twi_config_t), there's no where to set drive strength, only frequency, interrupt_priority and clear_bus_init.

So I added the following code to gpio_init():

nrf_gpio_cfg(CD_AUD_SDA, NRF_GPIO_PIN_DIR_OUTPUT, NRF_GPIO_PIN_INPUT_CONNECT, NRF_GPIO_PIN_NOPULL, NRF_GPIO_PIN_H0D1, NRF_GPIO_PIN_NOSENSE); nrf_gpio_pin_set(CD_AUD_SDA);

I played around nrf_gpio_pin_drive_t with H0H1, H0D1 and some other permutations, It didn't solve the SDA not driven to zero voltage problem. The waveform is still the same as shown previously.

And adding this code sometimes locks up the program.

So what's the right way to solve the SDA not driven to zero voltage problem?

Thanks.