Dear all,

Pushing the hardware to the limits, I came up with a question about the architecture of the microcontroller itself: Can two different instances of SPIM start a transfer EXACTLY at the same time?

(Not just work simultaneously like in https://devzone.nordicsemi.com/f/nordic-q-a/29760/nrf52840-spi-simultaneous-connection).

Description:

I am using a single nRF52840-DK, running to instances of SPIM: SPIM 1 and SPIM 2 at the same time.

SPIM 1 is triggered by the compare event of TIMER 1 and a PPI channel connects them both.

SPIM 2 is triggered in the callback function of TIMER 2, no PPI channels involved.

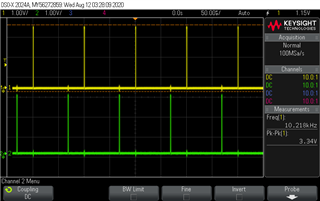

When I trigger TIMER 1 and 2 at 100 us, it works fine, like in the following picture. The pulses are the CLK signal of each SPIM, 16 bits each. I am quite sure the interrupts are generated at the same time but one is delayed due to the other one's priority, but that's good enough.

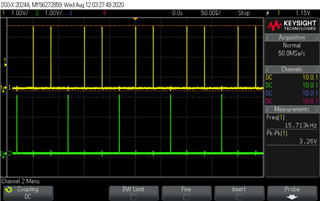

But ideally I would like TIMER 1 to tick every 100 us and TIMER 2 every 50 or 25 us. When I change that (SPIM 2 being the yellow trace), it looks like this, SPIM 2 triggering whenever SPIM 1 allows.

Since there are four possible instances of SPIM, I had the idea they would work independently, but checking the Product Specification (https://infocenter.nordicsemi.com/pdf/nRF52840_OPS_v0.5.pdf, page 12), the block diagram shows only one physical SPIM peripheral:

In a nutshell: Is it somehow possible to start more than one SPIM transfer at the same time (if so, how?), or only one SPIM transfer can be started because they share the same physical peripheral? Or another explanation?

Best regards,

Fran89