I'm using an nRF52840-Preview-DK board in a POC (Proof Of Concept) to convert an I2S-TDM bus to SPI.

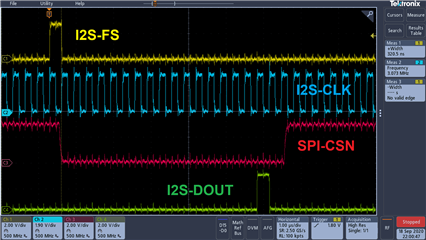

So it takes the I2S FS (frame sync) and CLK (clock) signals as inputs and generates the SPI CSN (chip select) signal

Then the I2S clock and data signals pass through unmodified to the SPI bus clock and data signals.

TIMER0 is in counter mode.

I have PPI setup so that:

- when FS goes high, CSN goes low and TIMER0 is cleared

- when CLK goes high, TIMER0 counts (TASK_COUNT)

- when TIMER0 COMPARE0 matches, CSN goes high

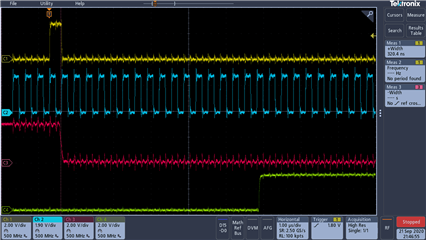

The problem is that when CSN goes high, about twice as many clocks have happened as expected, and its not always consistent. I'm testing with a CC0 of 10 and I'm seeing 17-20 clocks happening between CSN low and CSN high

So I suspect that the GPIOTE edge detection / TASK_COUNT is not keeping up.

CLK is running at 3.072MHz, so low-to-high edges happen every 326ns

I haven't found any specs on the max rate that the counter can count at.

What is that spec?