Hi,

I'm a beginner, and currently working to implement a low-power controller using nRF52-DK and Power Profiler Kit (PPK).

I ran the following codes (system off) and expected to see 0.3uA from the PPK as indicated in the nRF52832.

int main(void)

{

NRF_POWER->SYSTEMOFF = 1;

for(;;){}

}

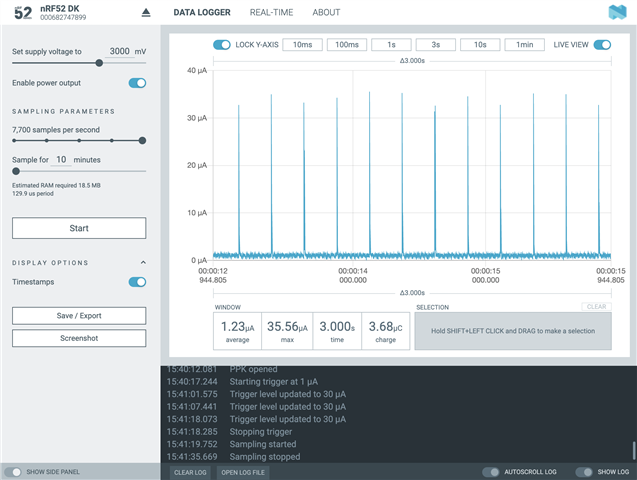

However, I could observe the periodic peak current of 36uA, so I'd like to know where it comes from.

Please note that I powered cycle the boards before measuring the current to make sure to have emulated system off.

Thank you in advance.