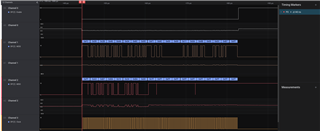

I am using nRF52840 DK and connecting it with SPI to ESP32. The first bit of the transmission is missed for some reason. I could verify that the transmission is ok with logic analyser:

But the data received by the nRF is:

<info> app: F8 B2 56 8D 4C 09 19 2B|..V.L .+

<info> app: E3 18 00 00 22 15 16 01|...."...

<info> app: B9 6F 00 00 00 00 00 00|.o......

<info> app: 00 00 00 00 00 00 00 00|........

<info> app: 00 00 00 00 00 00 00 00|........

<info> app: 00 00 00 00 00 00 00 00|........

<info> app: 00 00 00 00 00 00 00 00|........

<info> app: 00 00 00 00 00 00 00 00|........

<info> app: 00 00 00 00 00 00 00 00|........

<info> app: 00 00 00 00 00 00 00 00|........

I have checked mode and frequency setting and they all match. Also when I connect two nRFs (one Master and other Slave) they are having no issues when communicating this data.