nrf52832_qfaa_dcdcN.SchDocnrf52832_qfaa.PcbLibnrf52832_qfaa.SCHLIBnrf52832_qfax_dcdcN.PcbDoc

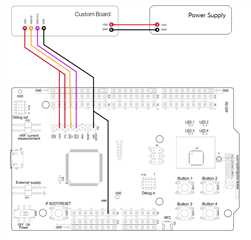

Hello, please review my PCB design for the nrf52832 soc. I think I've included all the necessary files, but let me know if you need anything else or something in a different format.

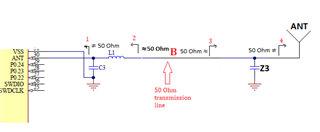

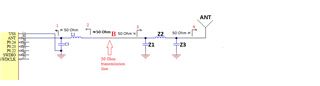

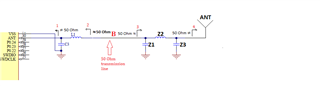

I used the nrf52832-QFAA Reference Layout DCDC as the base design for the PCB.

The changes I made were:

1.) Adding a 3.3V CR1632 battery to supply power to the 52832 as well as the PCF8523

2.) Added the PCF8523 RTC based off of the attached reference schematic from the adafruit PCF8523 development kit (https://cdn-learn.adafruit.com/downloads/pdf/adafruit-pcf8523-real-time-clock.pdf). Pin P0.22 will be configured SCL and pin P0.0.23 will be configured to SDA.

3.) Added a 5 pin header with connections for SWDIO, SWDCLK, VDD, GND, and Pin P0.14.

4.) Added a circuit to allow for attachment of a switch across pins 1 and 2 which will pull pin P0.14 to GND to use in software as a button press active low.

The overall goals are:

1.) Power the entire circuit and RTC with the CR1632 battery

2.) Use an external switch attached across header pins 1 and 2 to pull pin P0.14 to GND

3.) Get the time from the PCF8523 RTC upon button press over TWI using pins P0.22 and P0.23 as SCL and SDA

4.) Send the time over BLE

5.) Be able to program using header pins 2,3, 4 and 5.

Questions:

I know that it should be possible to program the chip with GND, VDD, SWDIO, SWDCLK but what programmer is specifically used for this type of programming? And is there functionality to program with this in Segger embedded studio?

I want to test the power consumption with the power profiler kit. It looks like the nrf52DK uses DCDC as its power regulator, so would testing the development kit power consumption be mostly representative of the power consumption of this PCB? How similar would the power consumption be between nrf52DK and this PCB?

I was looking into part sourcing and the X2 oscillator has 4 pads and is listed as XTAL SMD3215. I wasn't able to find any parts matching this description and was wondering if there was more information on sourcing a similar part. I was also wondering how closely the tolerance would have to match if an oscillator was substituted.

I also noticed that there wasn't a size description for the oscillators. Is this listed anywhere? I wasn't sure how to source the oscillators otherwise without replacing the footprint/pcb.

Thanks!

(meander, inverted F..+++ and chip antennas)

(meander, inverted F..+++ and chip antennas)