I'm struggling to get a Micron MT25QU128ABA (https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/nor-flash/serial-nor/mt25q/die-rev-a/mt25q_qlhs_u_128_aba_0.pdf) in QSPI mode. I'm positive all the pins are correctly configured and can read and write to the NOR Flash using fewer data lines

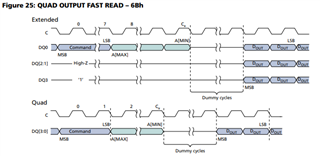

If I set #define QSPI_CONFIG_READOC 4 and #define QSPI_CONFIG_WRITEOC 3 in sdk_config.h, I can write just fine, but when reading back the data, it's shifted by 2 bytes (and the initial 2 bytes are 0x88). Which seems to be a misconfiguration of the NOR FLash registers. In order to fix it, I need to set #define QSPI_CONFIG_READOC 3, and everything works, but not in 4-4-4 mode.

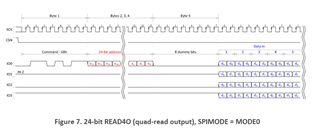

In order to enable 4-4-4 mode on the Micron chip, I need to set the correct bit in the volatile or non-volatile registers (different from how the NOR chip on the PCA10056 board works. But as soon as I enable the volatile register for 4-4-4, I cannot communicate with the chip anymore. It looks as if the CPU is sending commands on just one or 2 data lines and not really in 4-4-4 mode

I attached a logic analyzer [...]. EDIT: I now realize that the trace I included is not really representative (leaving it anyway for context). See next answer for more info. Please let me know if you need a specific trace and, if so, which commands and data would help

How can I enable 4-4-4? What am I doing wrong?