Hi, recently I'm looking at some computer architecture books.

So my question could be easy or silly.

I tried to search more but I couldn't find many.

The nRF51822 is based on Cortex-M0. So it has 56 instructions.

**/**************************************/

- Does every instructions (of this MCU, let's only limit it to Rev. 3) take the same time to complete it?

For example,

??main_1:

ADDS R0, R0, #1

??main_2:

CMP R0, #200

BLT.N ??main_1

suppose the time it takes to finish the ADDS, CMP, or BLT.N are t0, t1, t2.

Is t0 == t1 == t2? Or are they all different?

- If every instructions take the same amount of time, does that value equals to 1/14 usec?

I thought of this since nrf_delay_us function uses 14 instructions to delay 1 usec.

If not, what calculation made the developers to use 14 instructions to delay 1 usec?

- Continuing with the value of

t0, t1, t2, how much does it take?

Is it just 1 / clock frequency?

Since Cortex M0 uses 3-stage pipeline, do I have to consider this as well?

- When using

simple_uart_putstring()(located atsimple_uart_putstring.cSDK 7.2),

I wanted to know about the time gap after sending characters.

For instance,

#define MSG (const uint8_t *) "Hello\n"

int main(void){

//omit other parts...

uart_init(); // suppose the UART pin is initialized correctly without using HWID

// assume the baud rate is 115200, no parity, 8 bit data

while(true) simple_uart_putstring(MSG);

}

After sending 'H', could there be a small gap before sending 'e'?

Since simple_uart_putstring uses a while loop and increments,

I was wondering how much time will it take.

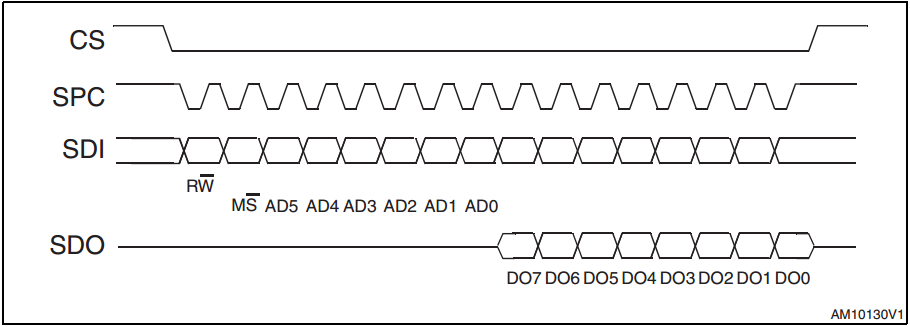

Added : Timing diagram of L3GD20.

-Regards, Mango922