Hi Everyone,

I have seen some posts regarding this topic on the forum but would just like to clarify a few things.

I am currently using an application timer to sample data from 4 channels @ 256 Hz. ( oversample = 4x, burst enabled on all channels, scan enabled ).

The application timer is currently configured at a default priority of 7 ( SDK v13 ).

The custom board I am using is configured as a BLE peripheral device and I understand that the radio interrupt has the highest priority.

Therefore, to minimize the effect of CPU blocking, the advertising interval has been set to be 1000 units ( 0.625ms/unit ).

The device will spent its majority of its operating time in advertising mode ( as opposed to connected )

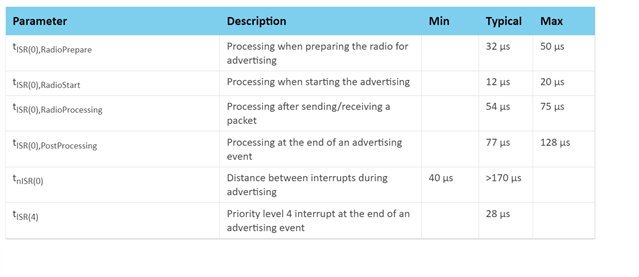

From the table taken from the documentation on BLE radio blocking time during advertisement shown below, it seems the maximum blocking time is 128us.

My first question is this, at 256Hz would this affect the sampling rate enough to warrant using PPI method to trigger ADC instead?

If so, how would I set up the ADC. Currently, I am thinking of using the spare RTC2 ( lower power than timer ), RCT0 and RTC1 are used by the

softdevice and application timer if my understanding is correct, to trigger the START task of the ADC with the compare event ( does RTC have a short clear like timer ? ).

Then to trigger the TASK_SAMPLE task with the STARTED event and once conversion has finished to trigger the STOP task, basically implementing the code shown in saadc_sample

function but with PPIs + tasks + events. So I would need in total of 4 PPIs ( 1 for timer, 3 for ADC )?

Would I then wait for the saadc interrupt function to be triggered and then process the data by filtering for EVENTS_END event only ( scan + oversample )?

If I implement the custom SAADC interrupt function using SAADC_IRQ, how do I clear the NVIC register?

The reason why I am not using the SAADC driver provided in SDK v13 is because the application needs to be as low power as possible.

And apparently with burst + oversample + scan mode enabled, a reset is needed on the ADC module after all samples have been taken in order to disable the DMA current.

Would I be able to implement this workaround using the PPI method described above?

The only method I can think of right now to implement the above, is to first call the unit function, then restart the ADC module and then call the init function within the ADC

interrupt handler. This will need to be done before timer triggers the next ADC Start task.

With the above implementation I presume there would be delay due to setting up DMA + actual acquisition time, but since this time is fixed for all samples the sampling rate would

be unaffected? ( eg, t(n) = t_setup + t_conver , t(n+1) = t_setup+t_conver+t_intervel (256Hz), t(n+1) - t(n) = t_interval ).

Could someone please verify if the above method is workable or suggest a better implementation?

Thanks!

SAADC sample function

static void saadc_sample()

{

NRF_SAADC->TASKS_START = 1;

while (NRF_SAADC->EVENTS_STARTED == 0);

NRF_SAADC->EVENTS_STARTED = 0;

// Do a SAADC sample, will put the result in the configured RAM buffer.

NRF_SAADC->TASKS_SAMPLE = 1;

while (NRF_SAADC->EVENTS_END == 0);

NRF_SAADC->EVENTS_END = 0;

NRF_SAADC->TASKS_STOP = 1;

saadc_uninit2();

*((volatile uint32_t *)0x40007FFC) = 0;

m_saadc_initialized = false;

}