I am using an STM32L4 chip that sends an update to the nRF52832 on a ublox module over USART. I assume the nordic chip is in the bootloader during the update.

We get a UART error: 4 and when we observe the UART lines we see that on the TX line of the nRF the stop bit is not present. I assume the nRF does not pull the line high properly after transmitting a frame. (we do not use pull-up resistors on the USART lines on STM32L4 side)

When trying to update with an OTA the device updates but then falls back into the bootloader at startup making me assume the problem is with the bootloader.

I am wondering if there is such documented cases of bootloader errors or if the missing stop bit could point to another issue with my HW/SW?

Thank you for any hint!

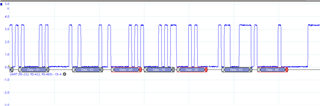

Bad behavior with missing stop bit:

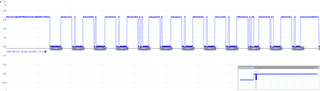

Good behavior with stop bit present:

Bad behavior with

-

blue: CTS

-

red: RTS

-

green: UART RX

-

yellow: UART TX