Hi,

Just wondered about the following ....

Strange parts of this code ... Or things I don't understand

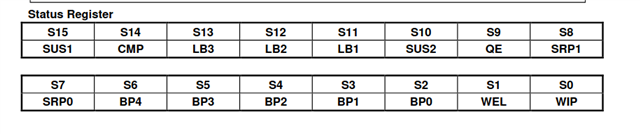

After the first READ in Setup() it successfully reads the data (Returns 0 = NRFX_SUCCESS), but the status flag

has the top 8 bits set to 0xFF which causes nrfx_qspi_mem_busy_check() to show 17 (Returns 17 = NRFX_ERROR_BUSY).

However masking the STATUS register with 8 reveals the Ready Status = 1, QSPI is ready!

This was why I wrote the QSPI_IsReady().

nrf_qspi_phy_conf_t not visible as a structure if you try and set it like this

QSPIConfig.phy_if {

.xxx = yyy,

.aaa = bbb

};

I don't know what the significance of the 48ms Deep Power-down Mode (DPM) is.

Will it go into DPM if not used for 48ms and then take 48ms to wake up if instructed?

Thanks

Paul