During development, I am seeing a strange behavior when enabling zigbee.

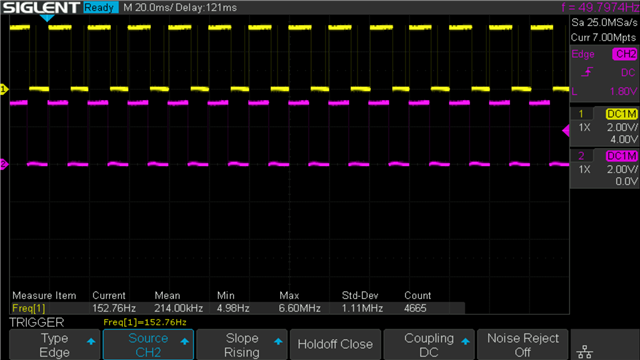

When the application's PRJ file does not enable zigbee, I2C functions as expected. The peripherals can be read and responses are received (as shown in the attached picture)

CONFIG_FPU=y CONFIG_SERIAL=y CONFIG_UART_INTERRUPT_DRIVEN=y CONFIG_EVENTS=y CONFIG_I2C=y CONFIG_NEWLIB_LIBC=y CONFIG_NEWLIB_LIBC_FLOAT_PRINTF=y CONFIG_AUDIO=y CONFIG_CMSIS_DSP=y CONFIG_CMSIS_DSP_TRANSFORM=y CONFIG_AUDIO_DMIC=y CONFIG_NRFX_TIMER1=y CONFIG_MPU_ALLOW_FLASH_WRITE=y CONFIG_FLASH=y CONFIG_FLASH_MAP=y CONFIG_FLASH_PAGE_LAYOUT=y CONFIG_FLASH_JESD216_API=y CONFIG_SPI=n CONFIG_SPI_NOR=n CONFIG_NORDIC_QSPI_NOR=y CONFIG_NORDIC_QSPI_NOR_FLASH_LAYOUT_PAGE_SIZE=4096 CONFIG_FILE_SYSTEM=y CONFIG_FILE_SYSTEM_LITTLEFS=y #CONFIG_APP_WIPE_STORAGE=y CONFIG_APP_LITTLEFS_STORAGE_FLASH=y # CONFIG_LOG=y # CONFIG_LOG_BACKEND_UART=n # CONFIG_LOG_MODE_MINIMAL=y # CONFIG_LOG_DEFAULT_LEVEL=0 CONFIG_HEAP_MEM_POOL_SIZE=8192 CONFIG_REBOOT=y

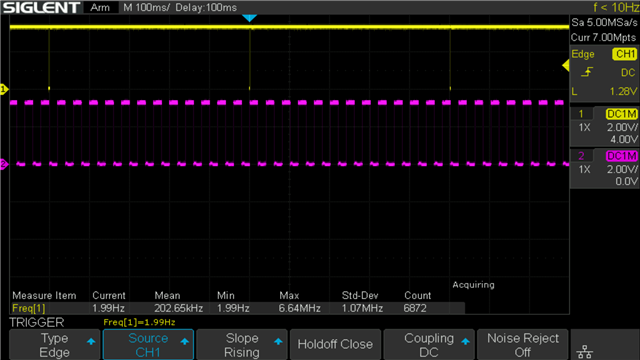

When Zigbee configurations are enabled (w/o even initializing Zboss) All comms on i2c3 time out.

CONFIG_FPU=y CONFIG_SERIAL=y CONFIG_UART_INTERRUPT_DRIVEN=y CONFIG_EVENTS=y CONFIG_I2C=y CONFIG_NEWLIB_LIBC=y CONFIG_NEWLIB_LIBC_FLOAT_PRINTF=y CONFIG_AUDIO=y CONFIG_AUDIO_DMIC=y CONFIG_HEAP_MEM_POOL_SIZE=32768 CONFIG_ZIGBEE=y CONFIG_ZIGBEE_APP_UTILS=y CONFIG_ZIGBEE_ROLE_END_DEVICE=y # Enable DK LED and Buttons library CONFIG_DK_LIBRARY=y # This example requires more workqueue stack CONFIG_SYSTEM_WORKQUEUE_STACK_SIZE=2048 # Enable API for powering down unused RAM parts CONFIG_RAM_POWER_DOWN_LIBRARY=y # Networking CONFIG_NET_IPV6_MLD=n CONFIG_NET_IPV6_NBR_CACHE=n CONFIG_NET_IPV6_RA_RDNSS=n CONFIG_NET_IP_ADDR_CHECK=n CONFIG_NET_UDP=n CONFIG_LOG=y CONFIG_LOG_DEFAULT_LEVEL=1 CONFIG_IEEE802154_DRIVER_LOG_LEVEL_INF=y CONFIG_NRF53_SYNC_RTC=n CONFIG_ASSERT=y CONFIG_SPIN_VALIDATE=y CONFIG_LOG_MODE_MINIMAL=n CONFIG_MAIN_STACK_SIZE=2048 # Use software cryptography on nRF5340 CONFIG_ZIGBEE_USE_SOFTWARE_AES=y # Networking CONFIG_MPSL=n CONFIG_NUM_COOP_PRIORITIES=20 CONFIG_NUM_PREEMPT_PRIORITIES=30 CONFIG_CMSIS_DSP=y CONFIG_CMSIS_DSP_TRANSFORM=y CONFIG_AUDIO_DMIC=y CONFIG_NRFX_TIMER1=y CONFIG_MPU_ALLOW_FLASH_WRITE=y CONFIG_FLASH=y CONFIG_FLASH_MAP=y CONFIG_FLASH_PAGE_LAYOUT=y CONFIG_FLASH_JESD216_API=y CONFIG_SPI=n CONFIG_SPI_NOR=n CONFIG_NORDIC_QSPI_NOR=y CONFIG_NORDIC_QSPI_NOR_FLASH_LAYOUT_PAGE_SIZE=4096 CONFIG_FILE_SYSTEM=y CONFIG_FILE_SYSTEM_LITTLEFS=y #CONFIG_APP_WIPE_STORAGE=y CONFIG_APP_LITTLEFS_STORAGE_FLASH=y # CONFIG_LOG=y # CONFIG_LOG_BACKEND_UART=n # CONFIG_LOG_MODE_MINIMAL=y # CONFIG_LOG_DEFAULT_LEVEL=0 CONFIG_REBOOT=y

Is there a known interaction between zigbee and I2C that prevents all I2C peripherals from bein used?