Dear Nordic Engineers

I have a question, it about SPI PIN input voltage of NRF5340.

Our cutsomer use NRF5340 and STM32 develop a product. STM32 and NRF5340 use SPI to communicate. NRF5340 is Master and STM32 is slave.

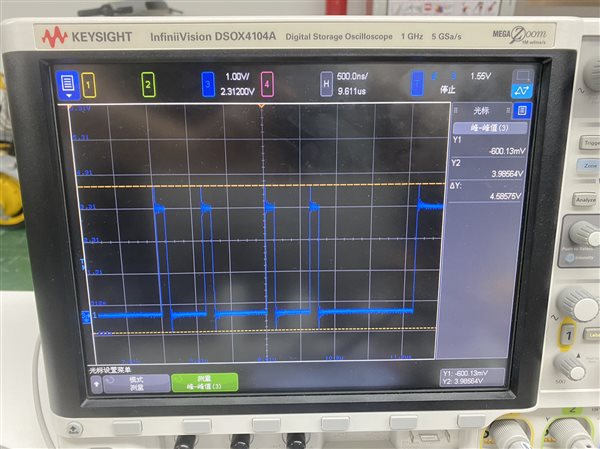

We found a problem that sometimes SPI data have chaos while they communicate. STM32 sending data to NRF5340 is chaos. We use Digital Storage Oscilloscope to test the MOSI pin of NRF5340,the wave of the MOSI pin is following.

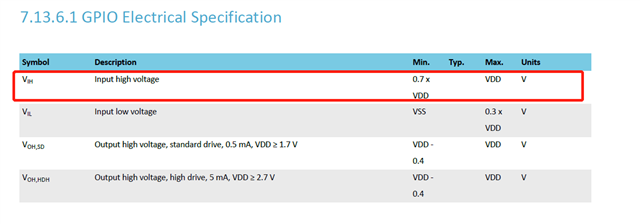

The peak of voltage is very high, it has 4V. As well all know, the max high voltage of GPIO input equal to VDD.

I would like to know this peak whether affect NRF5340 receive the SPI data.

Best regards,