Hi:

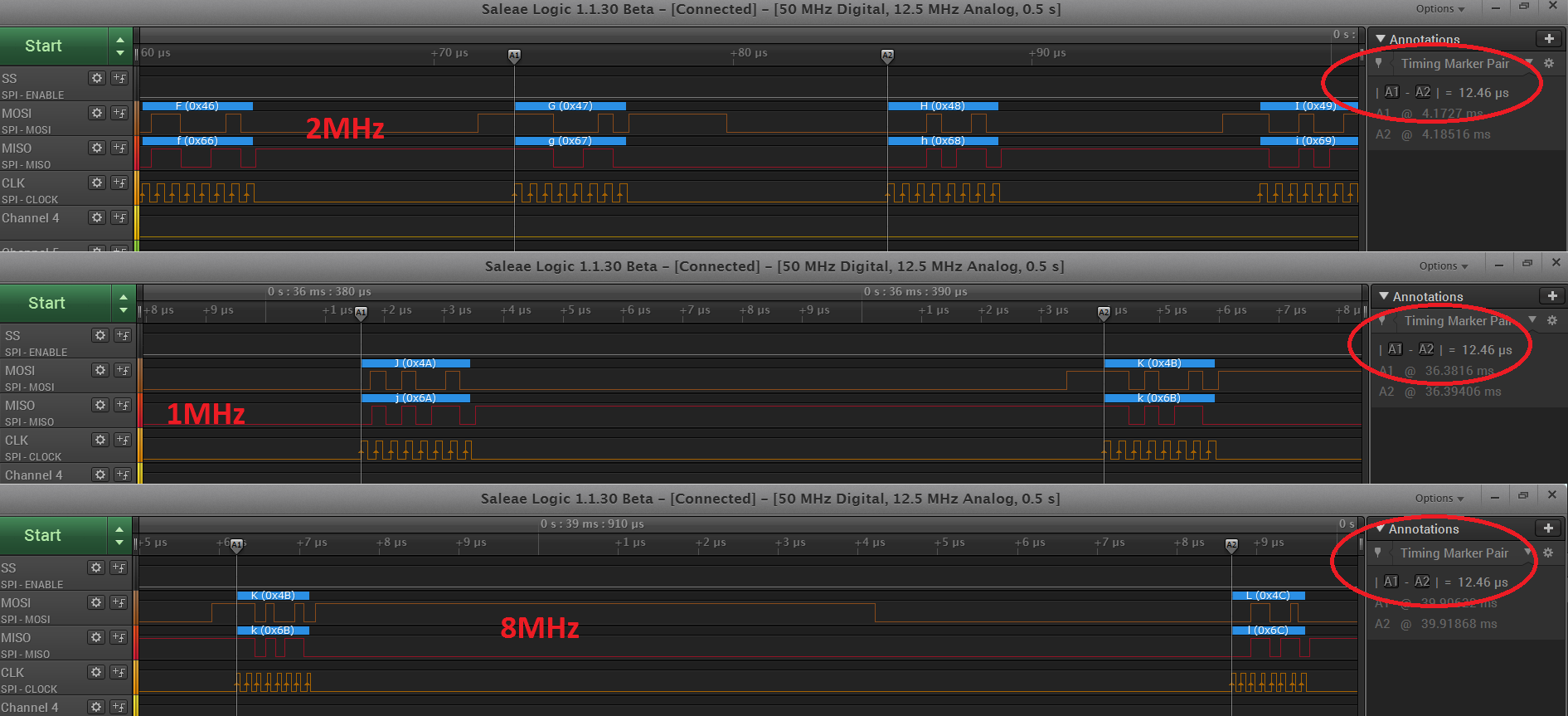

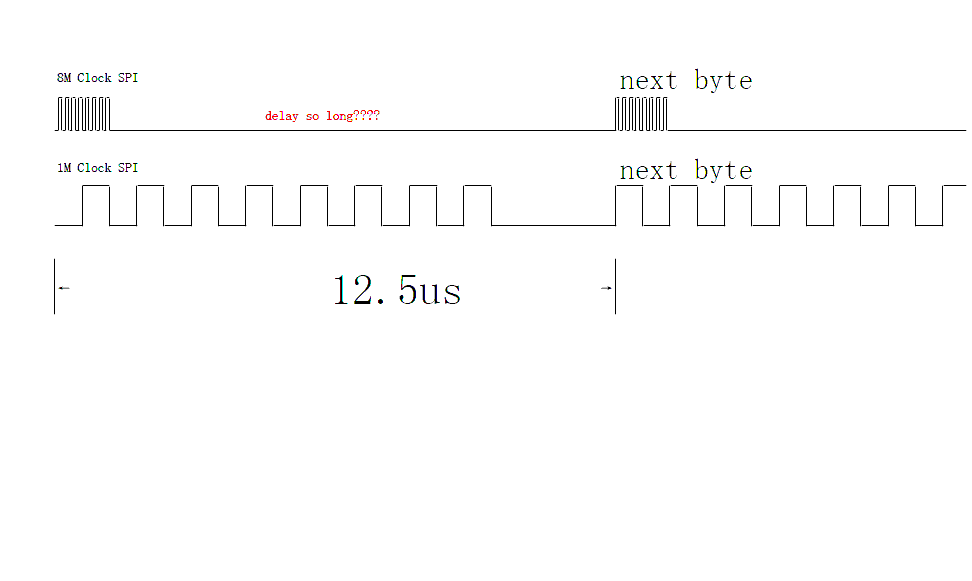

I use the demo code (nRF51_SDK_9.0.0_2e23562-NORDIC\nRF51_SDK_9.0.0_2e23562\examples\peripheral\spi_master) find a BUG(?) : when i use 1M clock , 1byte translate use about 10us, the delay between 2 byte is OK, when i use 4M clock , 1byte translate still use about 10us, the delay tbetween 2 byte is about 8us,

/@brief Macro for initializing SPI master by default values. /

#define SPI_MASTER_INIT_DEFAULT \

{ \ SPI_FREQUENCY_FREQUENCY_M1, /< Serial clock frequency 1 Mbps. */ \

SPI_PIN_DISCONNECTED, /< SCK pin DISCONNECTED. */ \

SPI_PIN_DISCONNECTED, /< MISO pin DISCONNECTED. */ \

SPI_PIN_DISCONNECTED, /< MOSI pin DISCONNECTED. */ \

SPI_PIN_DISCONNECTED, /< Slave select pin DISCONNECTED. */ \

APP_IRQ_PRIORITY_LOW, /< Interrupt priority LOW. */ \

SPI_CONFIG_ORDER_LsbFirst, /< Bits order LSB. */ \

SPI_CONFIG_CPOL_ActiveHigh, /< Serial clock polarity ACTIVEHIGH. */ \ SPI_CONFIG_CPHA_Leading, /< Serial clock phase LEADING. */ \

0 /*< Don't disable all IRQs. */ \

};