Hello,

I'm facing an issue with the behavior of the RAM state in the NRF52840 after a brownout reset.

Context: I've implemented a simple bootloop detection where a boot counter is incremented at the very beginning of each boot and cleared to 0 once our firmware initialization is over. During increment, the counter is checked against a maximal value, and if the counter reaches this maximal value, the firmware resets into the bootloader and waits for DFU. This allows a safety mode if the device is bricked and cannot boot properly. The boot counter is stored in a noinit region. This region is mapped in memory so that the reset handler won't reset it.

There are two ways to reset this counter:

1. Terminate the booting/initialization stage properly.

2. Have a full power on reset, as that will clear the RAM.

The problem I'm facing is that sometimes we have short power failures in our system, and this seems to disrupt the behavior of the anti-brick system. I have observed that if the power failure is too short in time, the boot counter is not reset to 0 but kept to the the last value.

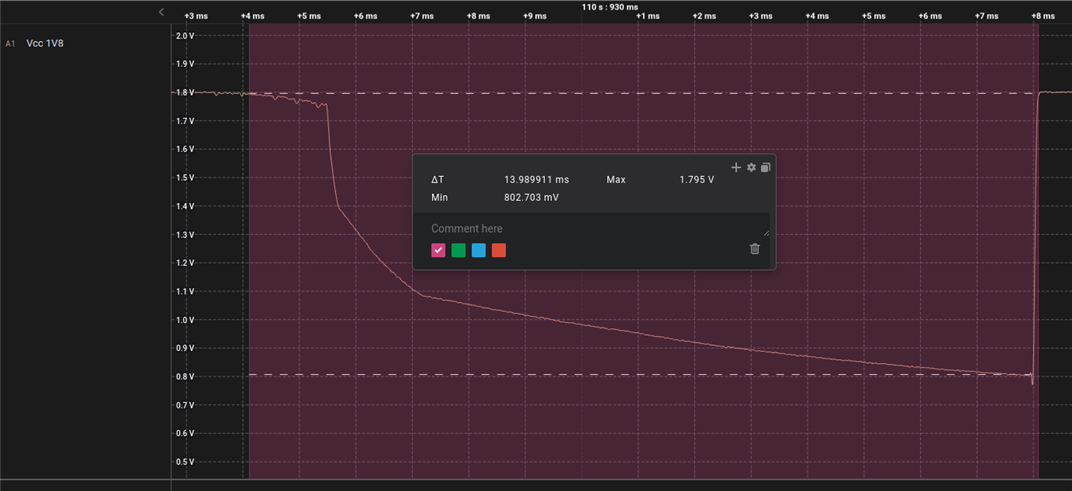

The MCU's Vdd is 1.8V. I've made some measurements where I can observe the issue.

In this measurement, we can see that the duration of the power outage is about 12.3 ms. Vdd starts at 1.8V, then drops to 800 mV, and then goes back to 1.8V.

Best

joël