Hello friends,

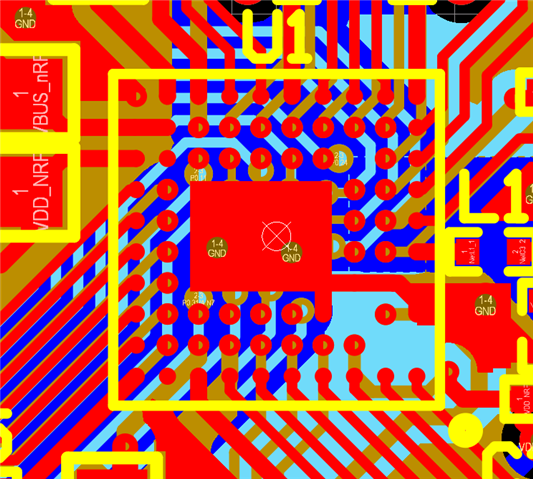

I am using nrf52840-CKAA for my customize PCB.

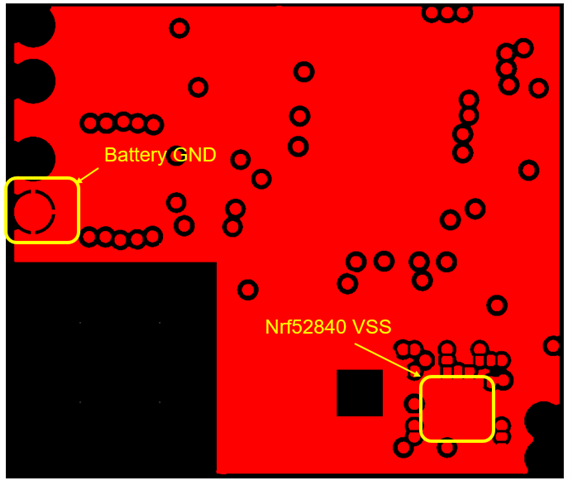

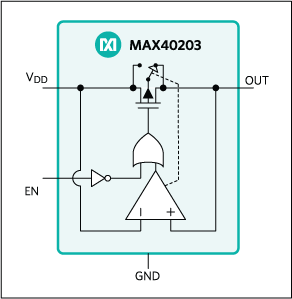

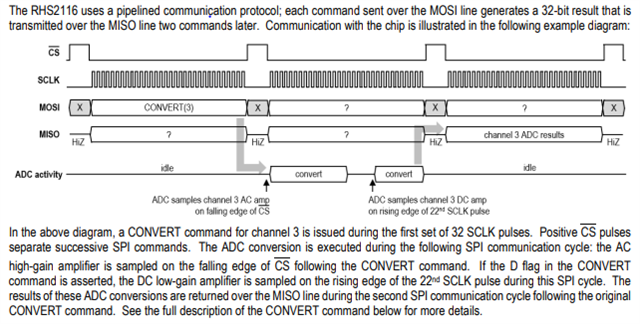

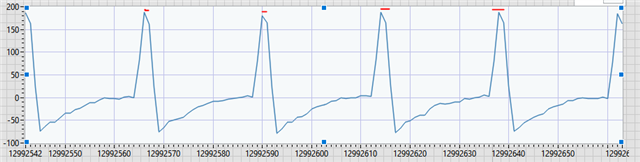

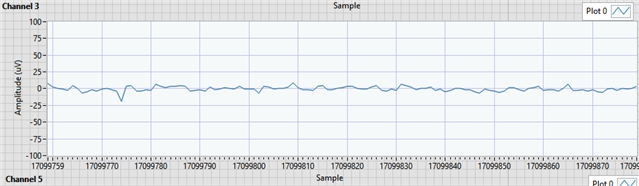

I am facing the noise during RF transmission on my ADC. The peak noise happen when I send a packet of data via RF antenna.

Power_Tx = 4dBm

When I decrease the Tx Power to -12dBm, the peak noise was gone.

I wonder that MCU takes a lot of power during RF transmission so it affect to the stability of power line.

In nrf52840-CKAA, currently I tie all VSS pin together instead of tie each of them directly to the GND plane. Is it the problem?

I appreciate all your suggestions.

Minhduc