Hi all,

Relatively quick question.

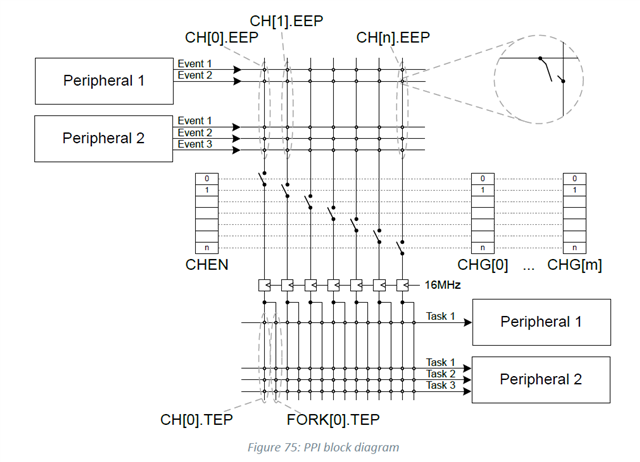

I have a production implementation where the COMP "Cross" event is wired by PPI to a GPIOTE "out" task.

The Comp is acting as a UVLO. When the GPIOTE is set off the voltage will rise and UVLO will turn it back on again. The thing at the other end of this is an LED buck driver, so fast to turn off but slow to turn on.

Previously I implemented using the COMP 'up and down' events PPI'd to the GPIOTE set/clr tasks. There was race issues and it didn't work hence the single PPI event approach. So long as an event isn't missed then the outputs are in sync with the COMP.

Recently I found events were occasionally, after a random time (could be an hour, could be minutes), being missed and it all went pear shaped. After investigation I found turning the COMP speed down from 'Normal' to 'Low' resolved the issue.

From the datasheet the COMP speed is

So what I know is either PPI or GPIOTE is unable to keep up at 0.2us, or 5MHz.

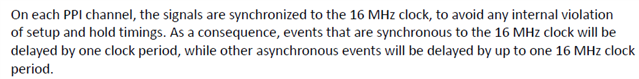

Which makes me curious, if PPI/GPIOTE aren't asynchronous they must be using a clock source. Which clock source? If it's the CPU will it be kept active during sleep/idle, in which case would the latency of doing the awake impact how quickly the event/task is processed and be the reason for the issue?

(I'm using CPU idle sleep but the level of work the CPU is doing changes which could be the reason for the randomness if the wake latency is a factor)

Thanks!